Page 88

Epson Research and Development

Vancouver Design Center

S1D13504

Hardware Functional Specification

X19A-A-002-19

Issue Date: 01/11/06

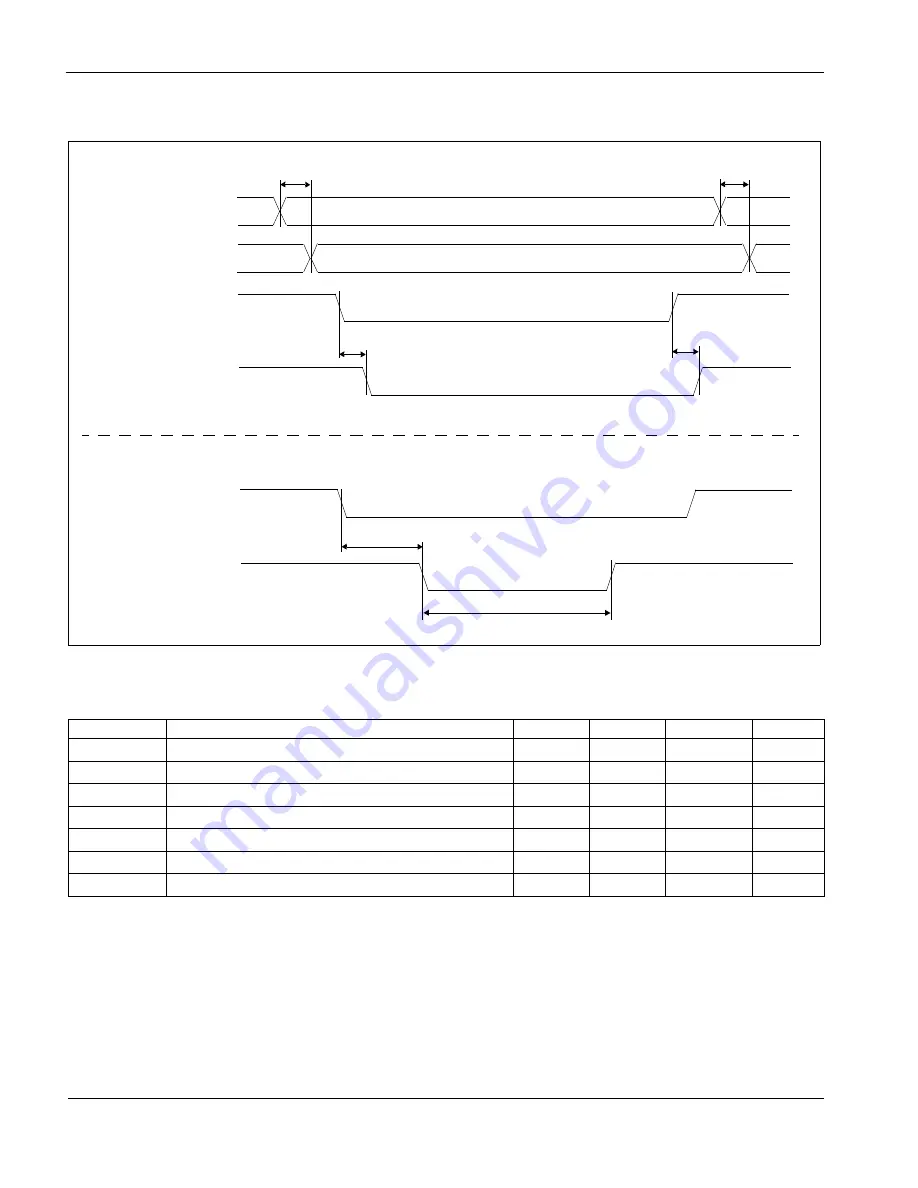

7.4.14 External RAMDAC Read / Write Timing

Figure 7-41: Generic Bus RAMDAC Read / Write Timing

Table 7-30:

Generic Bus RAMDAC Read / Write

Timing

Symbol

Parameter

Min Typ

Max

Units

T

BCLK

Bus clock period

30

ns

t1

AB[20:0], CS#, M/R# delay to DACRS[1:0]

10

ns

t2

DACRS[1:0] hold from AB[20:0], CS#, M/R# negated

10

ns

t3

Valid RD# command to DACRS[1:0] delay

8

33

ns

t4

DACRD# hold from valid RD# command negated

3

14

ns

t5

Valid WR# command to DACWR# delay

2 T

BCLK

ns

t6

DACWR# pulse width low

2.45 T

BCLK

2.55 T

BCLK

ns

AB[20:0]

Valid RD# Command

t1

DACRS[1:0]

t5

Write

t3

t4

DACRD#

t2

DACWR#

t6

Valid WR# command

Read

CS#

M/R#

(depends on CPU bus)

(depends on CPU bus)