Epson Research and Development

Page 89

Vancouver Design Center

Hardware Functional Specification

S1D13504

Issue Date: 01/11/06

X19A-A-002-19

8 Registers

8.1 Register Mapping

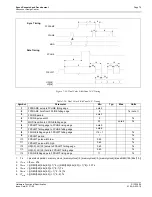

The S1D13504 registers are all memory mapped. The system must provide the external address

decoding through the CS# and M/R# input pins. When CS# = 0 and M/R# = 0, the registers are

mapped by address bits AB[5:0], e.g. REG[00h] is mapped to AB[5:0] = 000000, REG[01h] is

mapped to AB[5:0] = 000001. See the table below:

8.2 Register Descriptions

Note

Unless specified otherwise, all register bits are reset to 0 during power up. Reserved bits should

be written 0 when programming unless otherwise noted.

8.2.1 Revision Code Register

bits 7-2

Product Code Bits [5:0]

This is a read-only register that indicates the product code of the chip. The product code is 000001.

bits 1-0

Revision Code Bits [1:0]

This is a read-only register that indicates the revision code of the chip. The revision code is 00.

Table 8-1: S1D13504 Addressing

CS#

M/R#

Access

0

0

Register access:

• REG[00h] is addressed when AB[5:0] = 0

• REG[01h] is addressed when AB[5:0] = 1

• REG[n] is addressed when AB[5:0] = n

0

1

Memory access: the 2M byte display buffer is addressed by

AB[20:0]

1

X

S1D13504 not selected

Revision Code Register

REG[00h]

RO

Product Code

Bit 5

Product Code

Bit 4

Product Code

Bit 3

Product Code

Bit 2

Product Code

Bit 1

Product Code

Bit 0

Revision

Code Bit 1

Revision

Code Bit 0