Page 90

Epson Research and Development

Vancouver Design Center

S1D13504

Hardware Functional Specification

X19A-A-002-19

Issue Date: 01/11/06

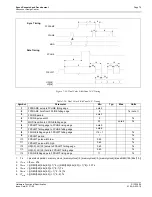

8.2.2 Memory Configuration Registers

bits 6-4

DRAM Refresh Rate Select Bits [2:0]

These bits specify the amount of divide from the input clock (CLKI) to generate the DRAM refresh

clock rate, which is equal to 2

(ValueOfThe 6)

.

bit 2

WE# Control

When this bit = 1, 2-WE# DRAM is selected. When this bit = 0 2-CAS# DRAM is selected.

bit 0

Memory Type

When this bit = 1, FPM-DRAM is selected. When this bit = 0, EDO-DRAM is selected.

This bit should be changed only when there are no read/write DRAM cycles. This condition occurs

when both the Display FIFO is disabled (REG[23h] bit 7 = 1) and the Half Frame Buffer is disabled

(REG[1Bh] bit 0 = 1). For programming information, see S1D13504 Programming Notes and

Examples, document number X19A-G-002-xx.

Memory Configuration Register

REG[01h]

RW

n/a

Refresh Rate

Bit 2

Refresh Rate

Bit 1

Refresh Rate

Bit 0

n/a

WE# Control

n/a

Memory Type

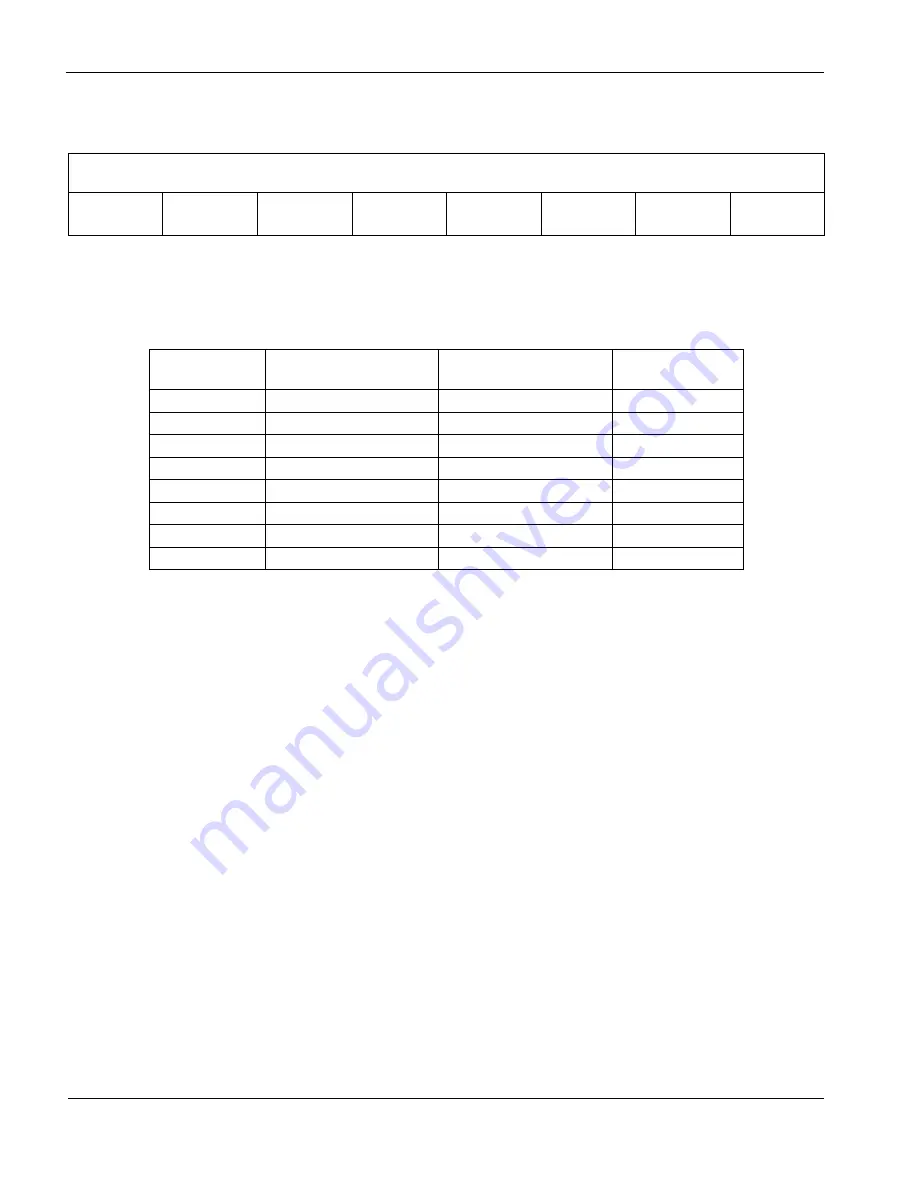

Table 8-2: DRAM Refresh Rate Selection

Refresh Rate

Bits [2:0]

CLKI Divide Amount

Refresh Rate for 33MHz

CLKI

DRAM Refresh

Time/256 Cycles

000

64

520 kHz

0.5 ms

001

128

260 kHz

1 ms

010

256

130 kHz

2 ms

011

512

65 kHz

4 ms

100

1024

33 kHz

8 ms

101

2048

16 kHz

16 ms

110

4096

8 kHz

32 ms

111

8192

4 kHz

64 ms