Page 30

Epson Research and Development

Vancouver Design Center

S1D13505

Programming Notes and Examples

X23A-G-003-07

Issue Date: 01/02/05

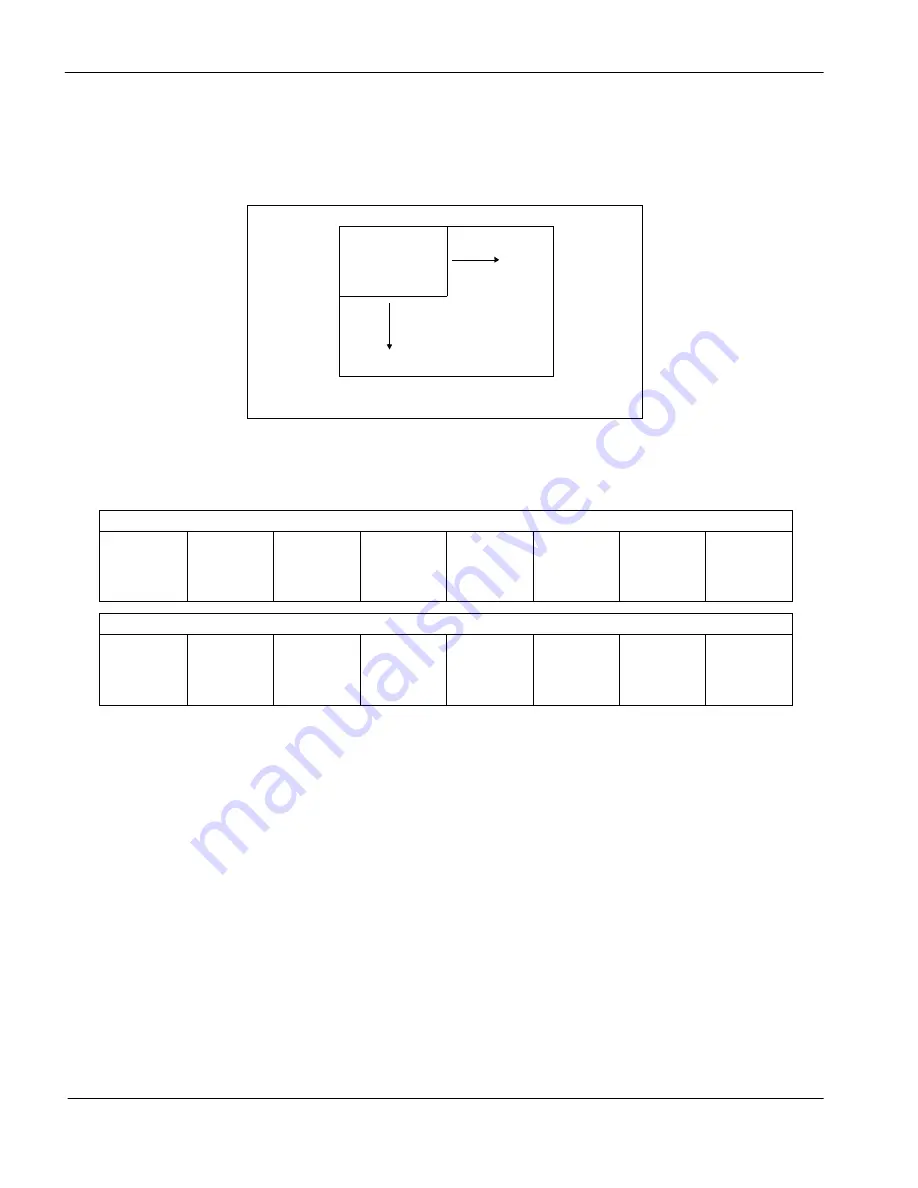

Seldom are the maximum sizes used. Figure 5-1: “Viewport Inside a Virtual Display,”

depicts a more typical use of a virtual display. The display panel is 320x240 pixels, an

image of 640x480 pixels can be viewed by navigating a 320x240 pixel viewport around the

image using panning and scrolling.

Figure 5-1: Viewport Inside a Virtual Display

5.1.1 Registers

Figure 5-2: Memory Address Offset Registers

Registers [16h] and [17h] form an 11-bit value called the memory address offset. This

offset is the number of words from the beginning of one line of the display to the beginning

of the next line of the display.

Note that this value does not necessarily represent the number of words to be shown on the

display. The display width is set in the Horizontal Display Width register. If the offset is set

to the same as the display width then there is no virtual width.

To maintain a constant virtual width as color depth changes, the memory address offset

must also change. At 1 bpp each word contains 16 pixels, at 16 bpp each word contains one

pixel. The formula to determine the value for these registers is:

offset = pixels_per_line / pixels_per_word

REG[16h] Memory Address Offset Register 0

Memory

Address

Offset

Bit 7

Memory

Address

Offset

Bit 6

Memory

Address

Offset

Bit 5

Memory

Address

Offset

Bit 4

Memory

Address

Offset

Bit 3

Memory

Address

Offset

Bit 2

Memory

Address

Offset

Bit 1

Memory

Address

Offset

Bit 0

REG[17h] Memory Address Offset Register 1

n/a

n/a

n/a

n/a

n/a

Memory

Address

Offset

Bit 10

Memory

Address

Offset

Bit 9

Memory

Address

Offset

Bit 8

320x240

Viewport

640x480

“Virtual” Display