Epson Research and Development

Page 39

Vancouver Design Center

Programming Notes and Examples

S1D13505

Issue Date: 01/02/05

X23A-G-003-07

Setting the LCD Enable bit to 0 causes the S1D13505 to disable the LCD display. The

following sequence of events occurs:

1. Disables the LCD power.

2. Counts 128 frames to wait for the LCD bias power supply to discharge.

3. Disables the LCD signals.

The LCD Power Disable bit is used to manually power-off the LCD bias power supply.

Setting the LCD Power Disable bit to 1 begins discharging the LCD bias power supply.

Setting the LCD Power Disable bit to 0 causes the LCD bias power supply to power-on.

If your situation requires using the LCD Power Disable bit, see Section 6.1.2, “LCD Power

Disable” on page 39 for the correct procedure. The LCD Enable bit (REG[0Dh] bit 0)

should be set to 1 to allow the S1D13505 to power-on the LCD using the automatic LCD

Power Sequencing.

6.1.2 LCD Power Disable

If the LCD bias power supply timing requirements are different than those timings built into

the S1D13505 power disable sequence, it may be necessary to manually power-off an LCD

panel. One of two situations may be true:

• Delay is too short.

• Delay is too long.

Different procedures should be used for each situation. Choose the appropriate procedure

based on your requirements from the following:

Delay Too Short

To lengthen the 128 frame delay on LCDPWR.

1. Set REG[1Ah] bit 3 to 1 - disable LCD Power.

2. Count 'x' Vertical Non-Display Periods.

'x' corresponds to the power supply discharge time converted to the equivalent vertical

non-display periods.

3. Set REG[0Dh] bit 0 to 0 - disable the LCD outputs.

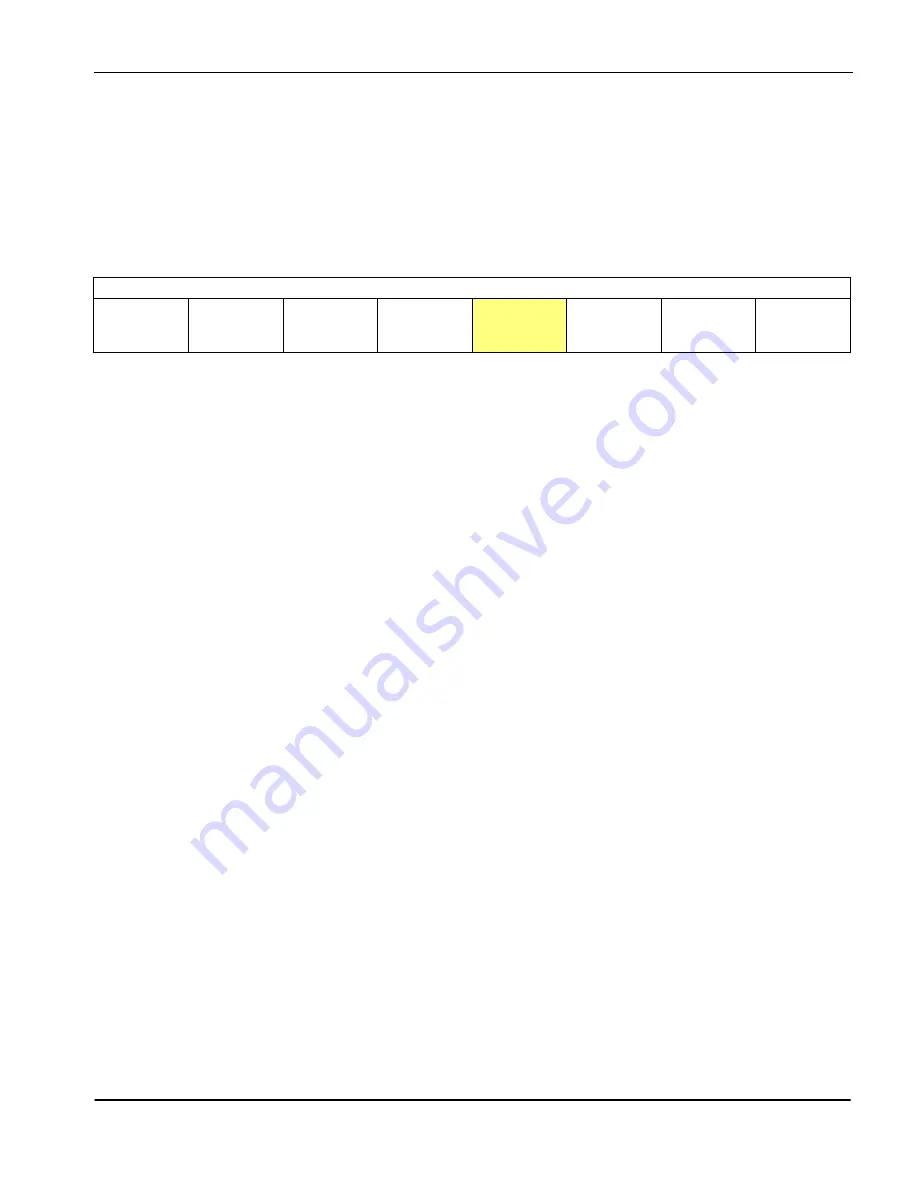

REG[1Ah] Power Save Configuration Register

Power Save

Status (RO)

n/a

n/a

n/a

LCD Power

Disable

Suspend

Refresh

Select Bit 1

Suspend

Refresh

Select Bit 0

Software

Suspend

Mode Enable