Epson Research and Development

Page 11

Vancouver Design Center

Programming Notes and Examples

S1D13704

Issue Date: 01/02/12

X26A-G-002-03

3 Memory Models

The S1D13704 is capable of operating at four different color depths. The data format for

each color depth is packed pixel. S1D13704 packed pixel modes can range from one byte

containing eight adjacent pixels (1-bpp) to one byte containing just one pixel (8-bpp).

Packed pixel data memory may be envisioned as a stream of data. Pixels fill this stream

with one pixel packed in adjacent to the next. If a pixel requires four bits then it will be

located in the four most significant bits of a byte. The pixel to the immediate right on the

display will occupy the lower four bits of the same byte. The next two pixels to the

immediate right are located in the following byte, etc.

3.1 Display Buffer Location

The S1D13704 contains 40 kilobytes of internal display memory. External support logic

must be employed to determine the starting address for this display memory in CPU address

space. On the S5U13704B00C PC platform evaluation boards the address is usually fixed

at D0000h.

3.1.1 1 Bit-Per-Pixel (2 Colors/Gray Shades)

1-bit pixels support two color/gray shades. In this memory format each byte of display

buffer contains eight adjacent pixels. Setting or resetting any pixel requires reading the

entire byte, masking out appropriate bits and, if necessary, setting bits to "1".

With color panels the two colors are derived by indexing into positions 0 and 1 of the Look-

Up Table. For monochrome panels the two gray shades are generated by indexing into the

first two elements of the green component of the Look-Up Table (LUT).

If the first two LUT elements are set to black (RGB = 0 0 0) and white (RGB = F F F) then

each "0" bit of display memory will display as a black pixel and each "1" bit will display as

a white pixel. The two LUT entries can be set to any desired colors, for instance red/green

or cyan/yellow.

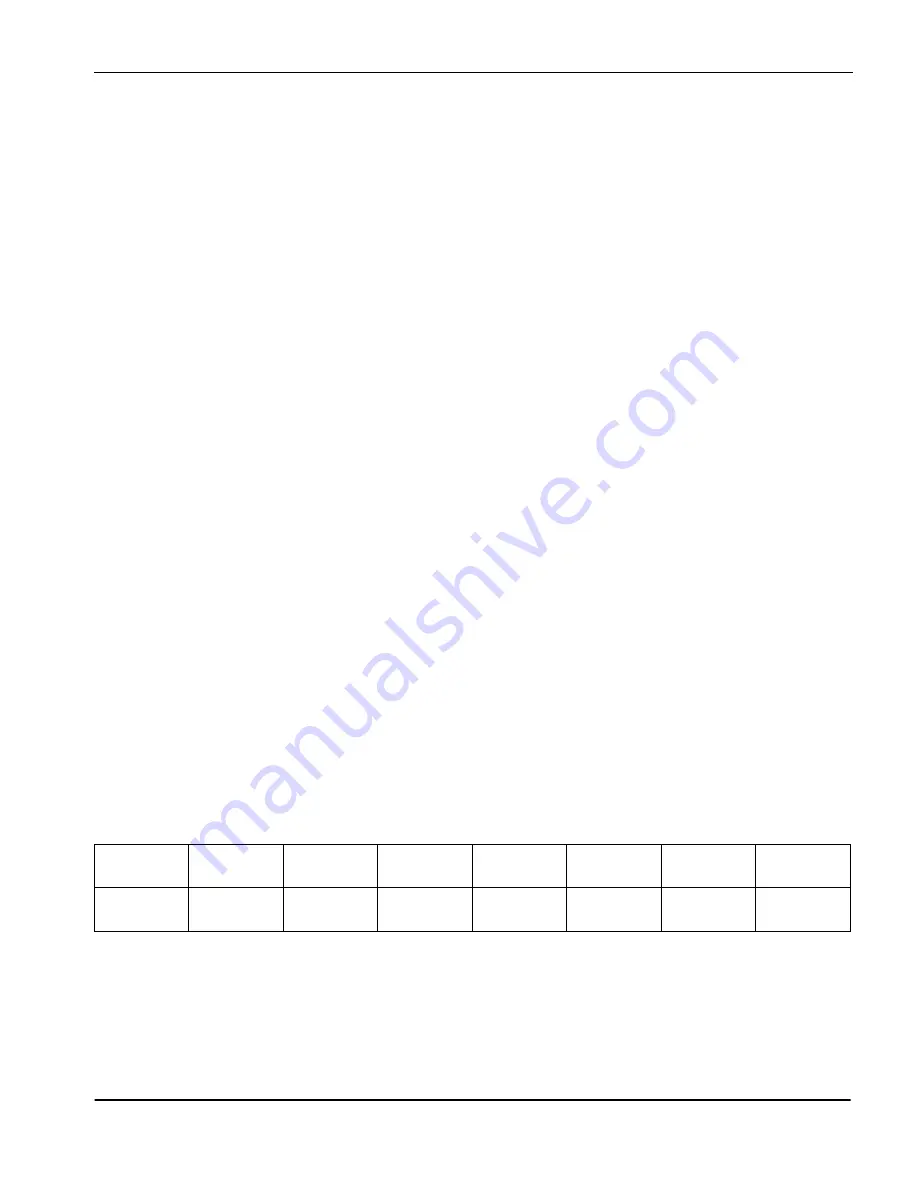

Figure 3-1: Pixel Storage for 1 Bpp (2 Colors/Gray Shades) in One Byte of Display Buffer

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Pixel 0

Pixel 1

Pixel 2

Pixel 3

Pixel 4

Pixel 5

Pixel 6

Pixel 7

*