Page 10

EPSON Research and Development

Vancouver Design Center

S1D13704

Interfacing to the Toshiba MIPS TX3912 Processor

X26A-G-004-02

Issue Date: 01/02/12

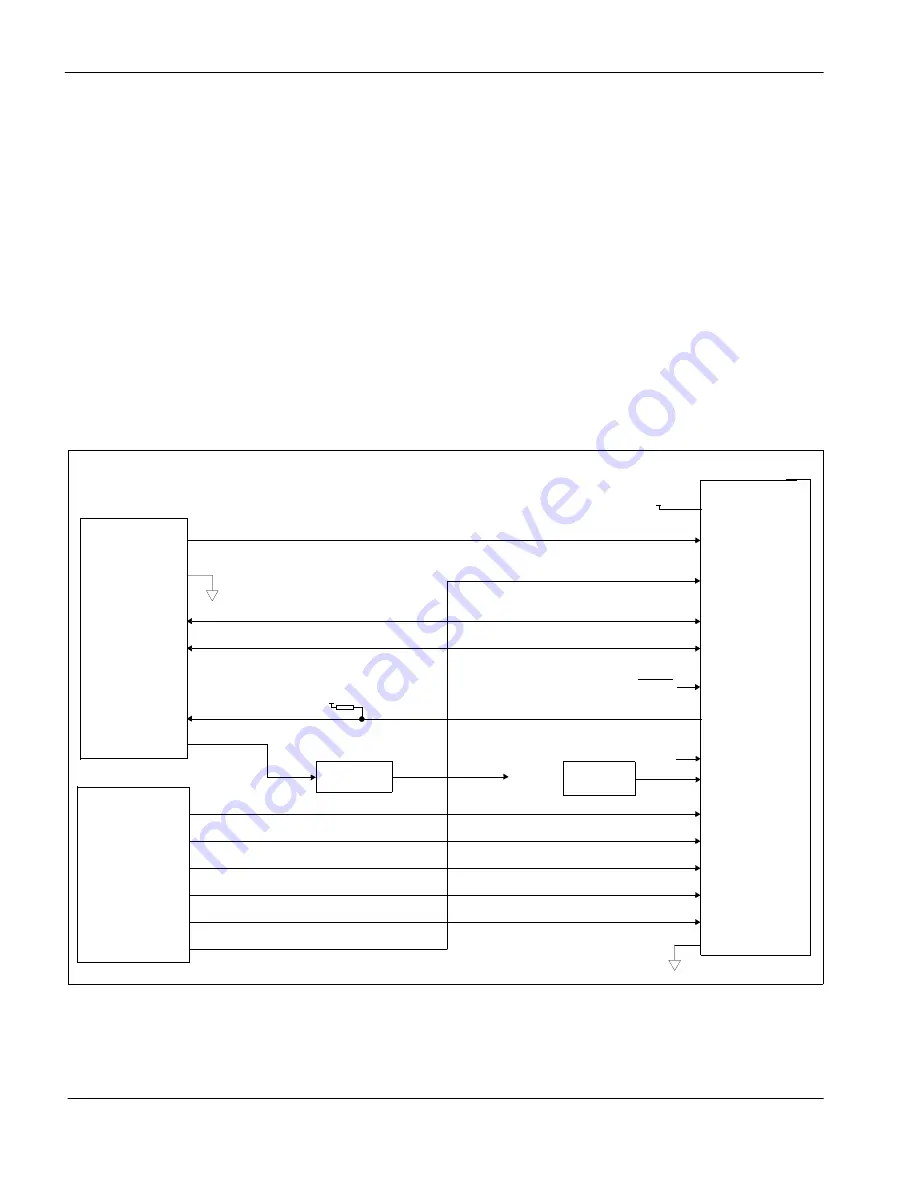

3 System Design Using the ITE IT8368E PC Card Buff er

If the system designer uses the ITE IT8368E PC Card and multiple-function I/O buffer, the

S1D13704 can be interfaced so that it ’shares’ a PC Card slot. The S1D13704 is mapped to a rarely-

used 16M byte portion of the PC Card slot buffered by the IT8368E. This makes the S1D13704

virtually transparent to PC Card devices that use the same slot.

3.1 Hardware Description

The ITE8368E has been specially designed to support EPSON LCD controllers. The ITE IT8368E

provides eleven Multi-Function IO pins (MFIO). Configuration registers may be used to allow these

MFIO pins to provide the control signals required to implement the S1D13704 CPU interface.

The TX3912 processor only provides addresses A[12:0], therefore devices requiring more address

space must use an external device to latch A[25:13]. The IT8368E’s MFIO pins can be configured

to provide this latched address.

Figure 3-1: S1D13704 to TX3912 Connection Using an IT8368E

IT8368E

S1D13704

HA[12:0]

AB[12:0]

HD[31:24]

DB[7:0]

LHA[23]/MFIO[10]

WE1#

WE0#

RD1#

RD0#

CS#

LHA[22]/MFIO[9]

LHA[21]/MFIO[8]

LHA[20]/MFIO[7]

LHA[19]/MFIO[6]

WAIT#

CARDxWAIT*

RESET#

AB[15:13]

TX3912

HD[23:16]

DB[15:8]

DCLKOUT

ENDIAN

System RESET

LHA[15:13]/

Oscillator

...or...

pull-up

V

DD

BCLK

CLKI

See text

Clock divider

BS#

IO V

DD

, CORE V

DD

+3.3V

MFIO[2:0]

*