Page 28

Epson Research and Development

Vancouver Design Center

S1D13704

Hardware Functional Specification

X26A-A-001-04

Issue Date: 01/02/08

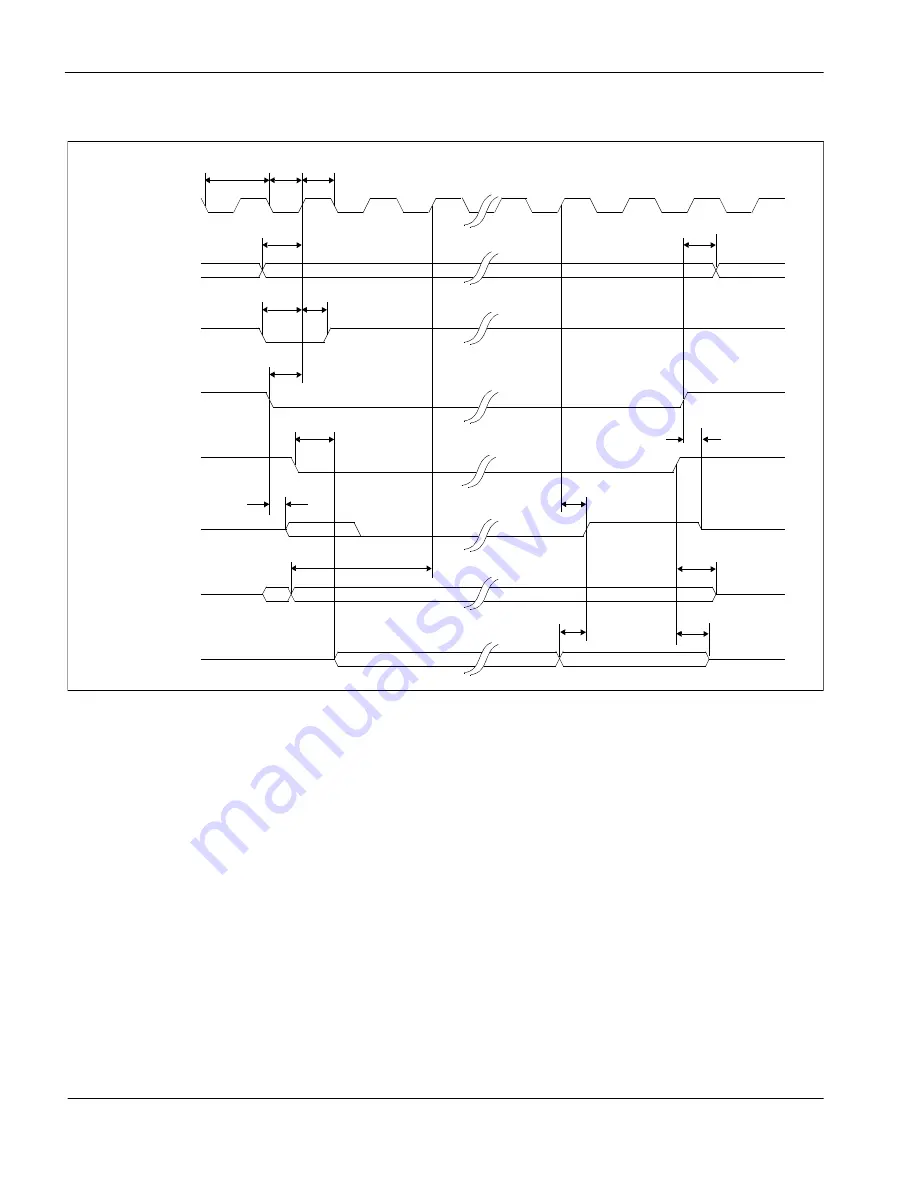

7.1.2 SH-3 Interface Timing

Figure 7-2: SH-3 Bus Timing

Note

The SH-3 Wait State Control Register for the area in which the S1D13704 resides must

be set to a non-zero value.

T

CKIO

t2

t3

t4

t10

t11

t15

t5

t6

t7

t8

t9

t12

t16

t13

t14

CKIO

A[16:0], M/R#

CSn#

RD/WR#

RD#

D[15:0]

BS#

WAIT#

WEn#

D[15:0]

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

VALID

(write)

(read)

*