Page 34

Epson Research and Development

Vancouver Design Center

S1D13704

Hardware Functional Specification

X26A-A-001-04

Issue Date: 01/02/08

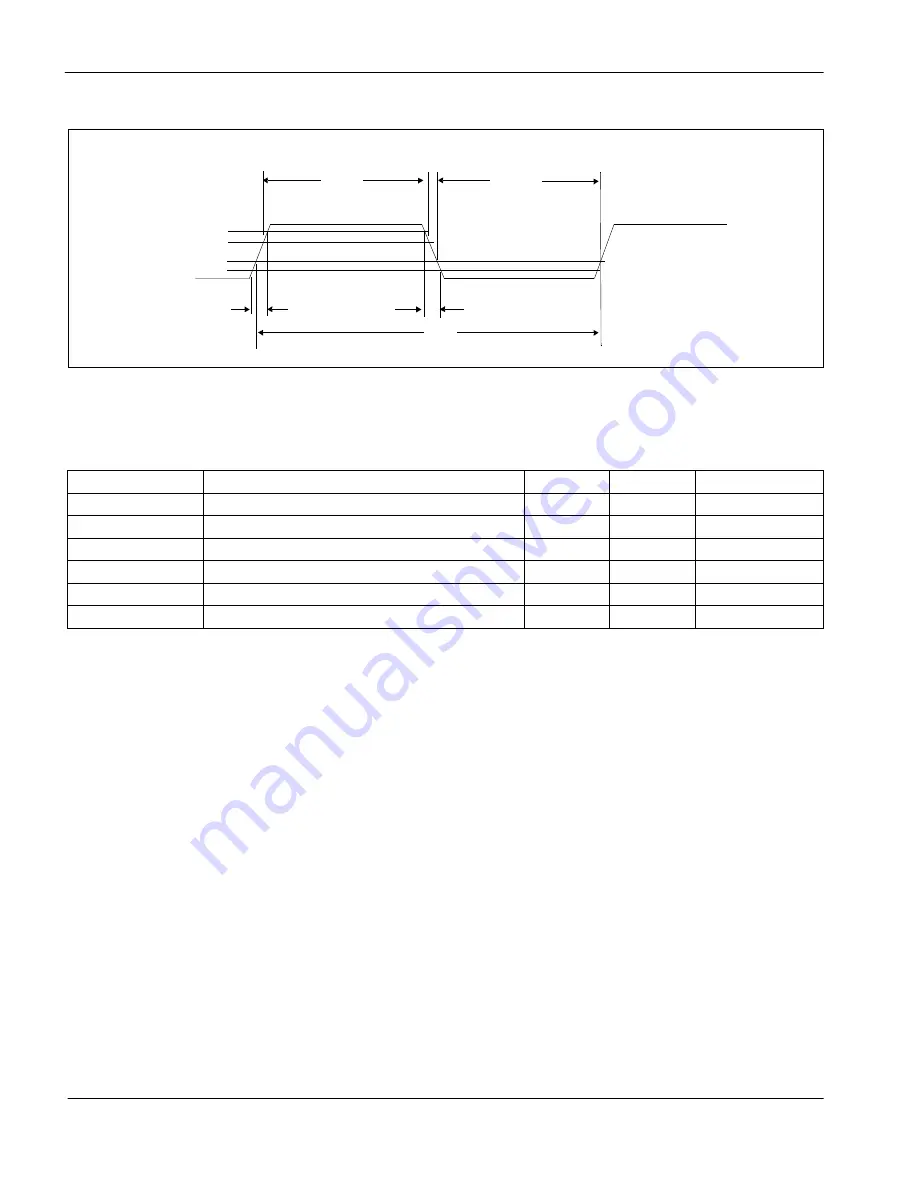

7.2 Clock Input Requirements

Figure 7-7: Clock Input Requirements

Note

When CLKI is > 25MHz it must be divided by 2 (REG[02h] bit 4 = 1).

Table 7-7: Clock Input Requirements

Symbol

Parameter

Min

Max

Units

f

CLKI

Input Clock Frequency (CLKI)

0

50

MHz

T

CLKI

Input Clock period (CLKI)

1/f

CLKI

t

PWH

Input Clock Pulse Width High (CLKI)

8

ns

t

PWL

Input Clock Pulse Width Low (CLKI)

8

ns

t

f

Input Clock Fall Time (10% - 90%)

5

ns

t

r

Input Clock Rise Time (10% - 90%)

5

ns

t

PWL

t

PWH

t

f

Clock Input Waveform

tr

T

CLKI

V

IH

VIL

10%

90%

*