Page 56

Epson Research and Development

Vancouver Design Center

S1D13704

Hardware Functional Specification

X26A-A-001-04

Issue Date: 01/02/08

bits 7-6

Bit-Per-Pixel Bits [1:0]

These bits select the color or gray-shade depth (Display Mode).

bit 5

High Performance (Landscape Modes Only)

When this bit = 0, the internal Memory clock (MCLK) is a divided-down version of the

Pixel clock (PCLK). The denominator is dependent on the bit-per-pixel mode - see the

table below.

When this bit = 1, MCLK is fixed to the same frequency as PCLK for all bit-per-pixel

modes. This provides a faster screen update performance in 1, 2, 4 bit-per-pixel modes, but

also increases power consumption. This bit can be set to 1 just before a major screen

update, then set back to 0 to save power after the update. This bit has no effect in Swivel-

View mode. Refer to REG[1Bh] SwivelView Mode Register on page 68 for SwivelView

mode clock selection.

REG[02h] Mode Register 1

Address = FFE2h

Read/Write.

Bit-Per-Pixel

Bit 1

Bit-Per-Pixel

Bit 0

High

Performance

Input Clock

divide

(CLKI/2)

Display Blank

Frame

Repeat

Hardware

Video Invert

Enable

Software

Video Invert

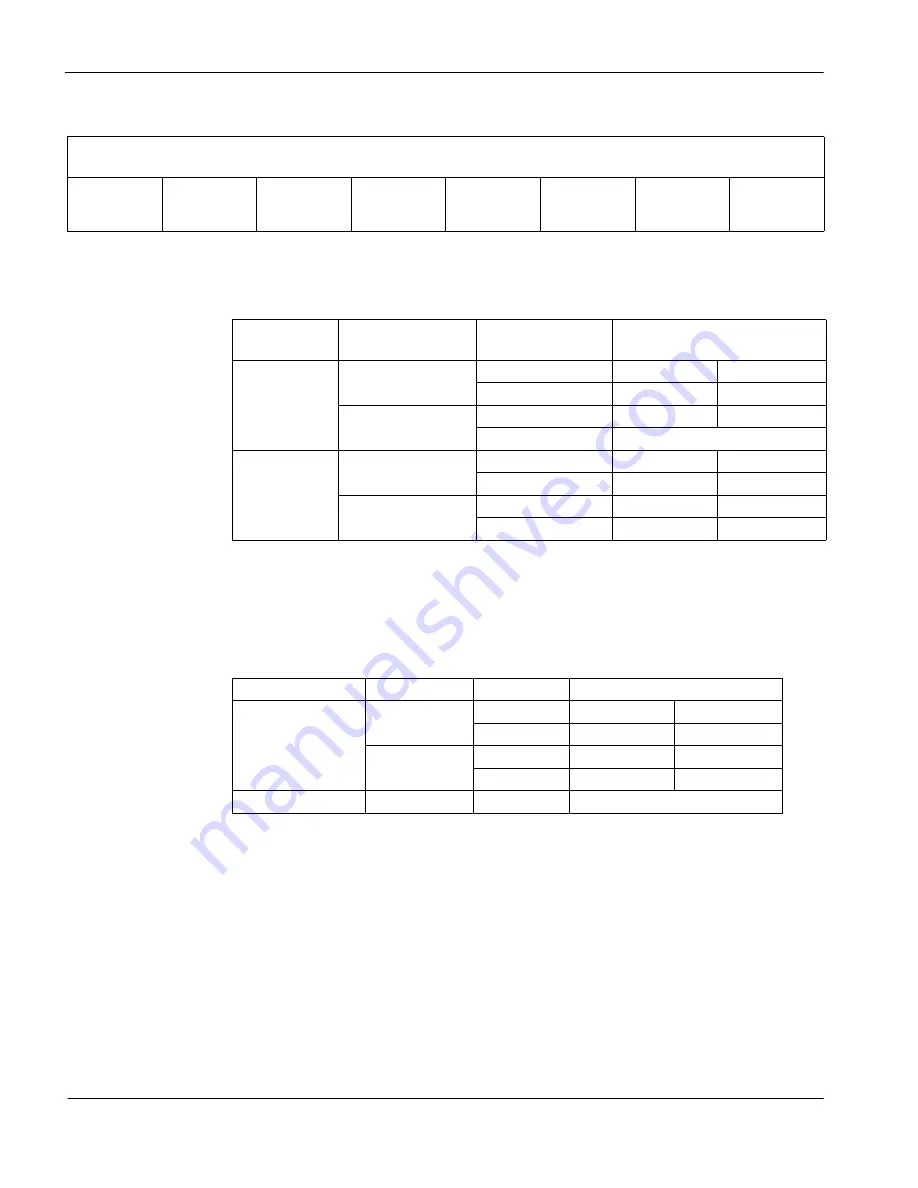

Table 8-2: Gray Shade/Color Mode Selection

Color/Mono

REG[01h] bit 6

Bit-Per-Pixel Bit 1

REG[02h] bit 7

Bit-Per-Pixel Bit 0

REG[02h] bit 6

Display Mode

0

0

0

2 Gray shade

1 bit-per-pixel

1

4 Gray shade

2 bit-per-pixel

1

0

16 Gray shade

4 bit-per-pixel

1

reserved

1

0

0

2 Colors

1 bit-per-pixel

1

4 Colors

2 bit-per-pixel

1

0

16 Colors

4 bit-per-pixel

1

256 Colors

8 bit-per-pixel

Table 8-3: High Performance Selection

High Performance

BPP Bit 1

BPP Bit 0

Display Modes

0

0

0

MClk = PClk/8

1 bit-per-pixel

1

MClk = PClk/4

2 bit-per-pixel

1

0

MClk = PClk/2

4 bit-per-pixel

1

MClk = PClk

8 bit-per-pixel

1

X

X

MClk = PClk

*