Page 8

Epson Research and Development

Vancouver Design Center

S1D13704

Programming Notes and Examples

X26A-G-002-03

Issue Date: 01/02/12

2 Initialization

This section describes the register settings and steps needed to initialize the S1D13704. The

first step toward initializing the S1D13704 is to set the control registers. The S1D13704

then generates the proper control signals for the display. After setting the control registers,

the Look-up Table must be programmed with meaningful values. This section does not

cover setting Look-Up Table values. See Section 4 on page 14 of this manual for Look-up

Table programming details.

The following initialization, presented in table form, provides the sequences and values to

set the registers. The notes column comments the reason for the particular value being

written.

This example writes to all the control registers. In practice, it may be possible to write to

only a subset of the registers. When the S1D13704 is first powered up all registers, unless

noted otherwise in the specification, are set to zero. This example programs these registers

to zero to establish a known state.

The initialization enables the S1D13704 to control a panel with the following specifica-

tions:

• 320x240 color dual passive panel at 75Hz.

• Color Format 2, 8-bit data interface.

• 4 bit-per-pixel (bpp) - 16 colors.

• 25 MHz input clock (CLKI).

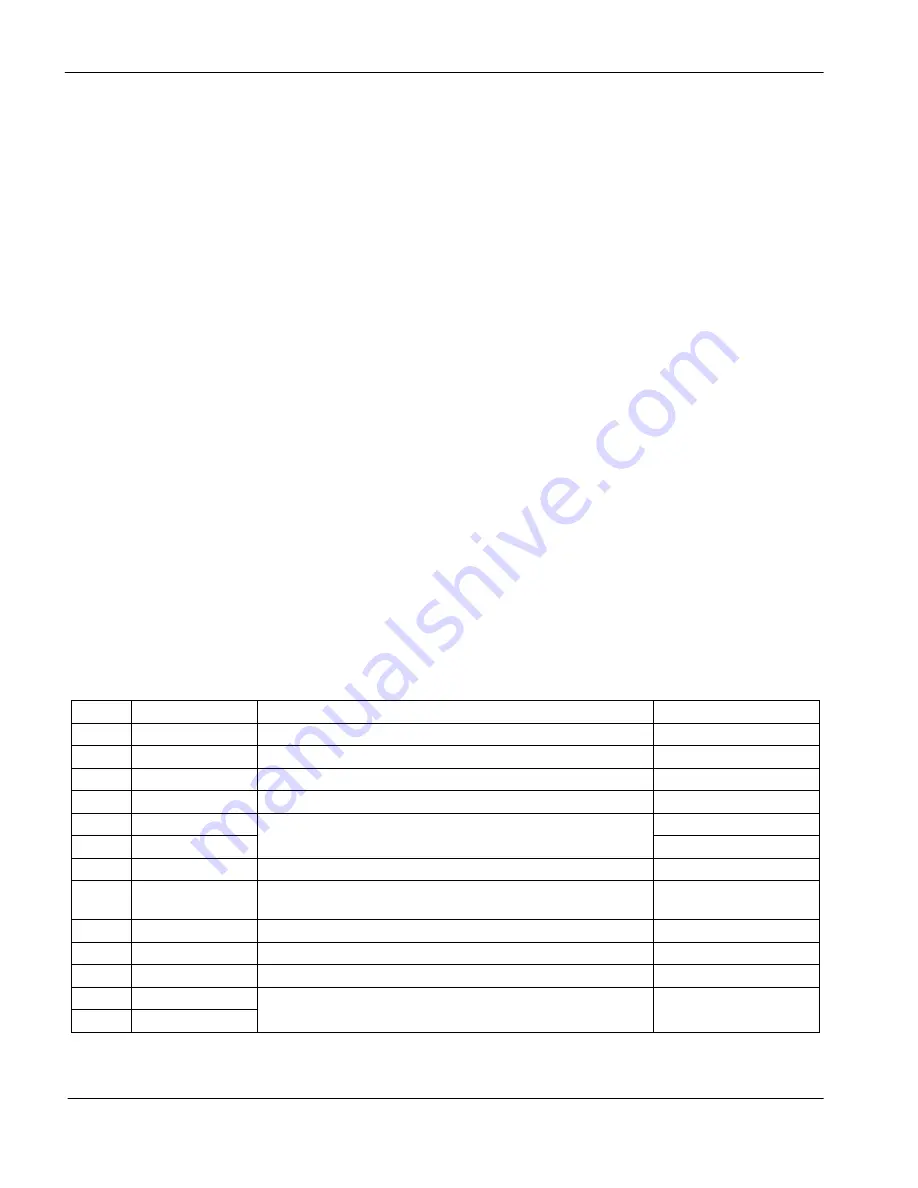

Table 2-1: S1D13704 Initialization Sequence

Register

Value (hex)

Notes

See Also

[01]

0010 0000 (20)

Select an passive, Single, Color panel with a data width of 4-bits

[02]

1010 0000 (B0)

Select 4-bpp color depth and high performance.

[03]

0000 0011 (03)

Select normal power operation

[04]

0010 0111 (27)

Horizontal display size = (Reg[04]+1)*8 = (39+1) * 8 = 320 pixels

[05]

1110 1111 (EF)

Vertical display size = Reg[06][05] + 1

= 0000 0000 1110 1111 + 1 = 239 +1 = 240 lines

[06]

0000 0000 (00)

[07]

0000 0000 (00)

FPLINE start position (not used by STN)

[08]

0001 1110 (1E)

Horizontal non-display period = (Reg[08] + 4) * 8

= (30 + 4) * 8 = 272 pixels

Frame Rate Calculation

[09]

0000 0000 (00)

FPFRAME start position (not used by STN)

[0A]

0010 0110 (26)

Vertical non-display period = REG[0A] = 38 lines

Frame Rate Calculation

[0B]

0000 0000 (00)

MOD rate - not required for this panel

[0C]

0000 0000 (00)

Screen 1 Start Address - set to 0 for initialization

[0D]

0000 0000 (00)

*