Epson Research and Development

Page 31

Vancouver Design Center

Programming Notes and Examples

S1D13704

Issue Date: 01/02/12

X26A-G-002-03

5.3.1 Registers

The other registers required for split screen operations, REG[0Ch] through REG[0Dh]

(Screen 1 Start Word Address) and REG[0Fh] through REG[10h] (Screen 2 Start Word

Address) are described in Section 5.2.1 on page 28.

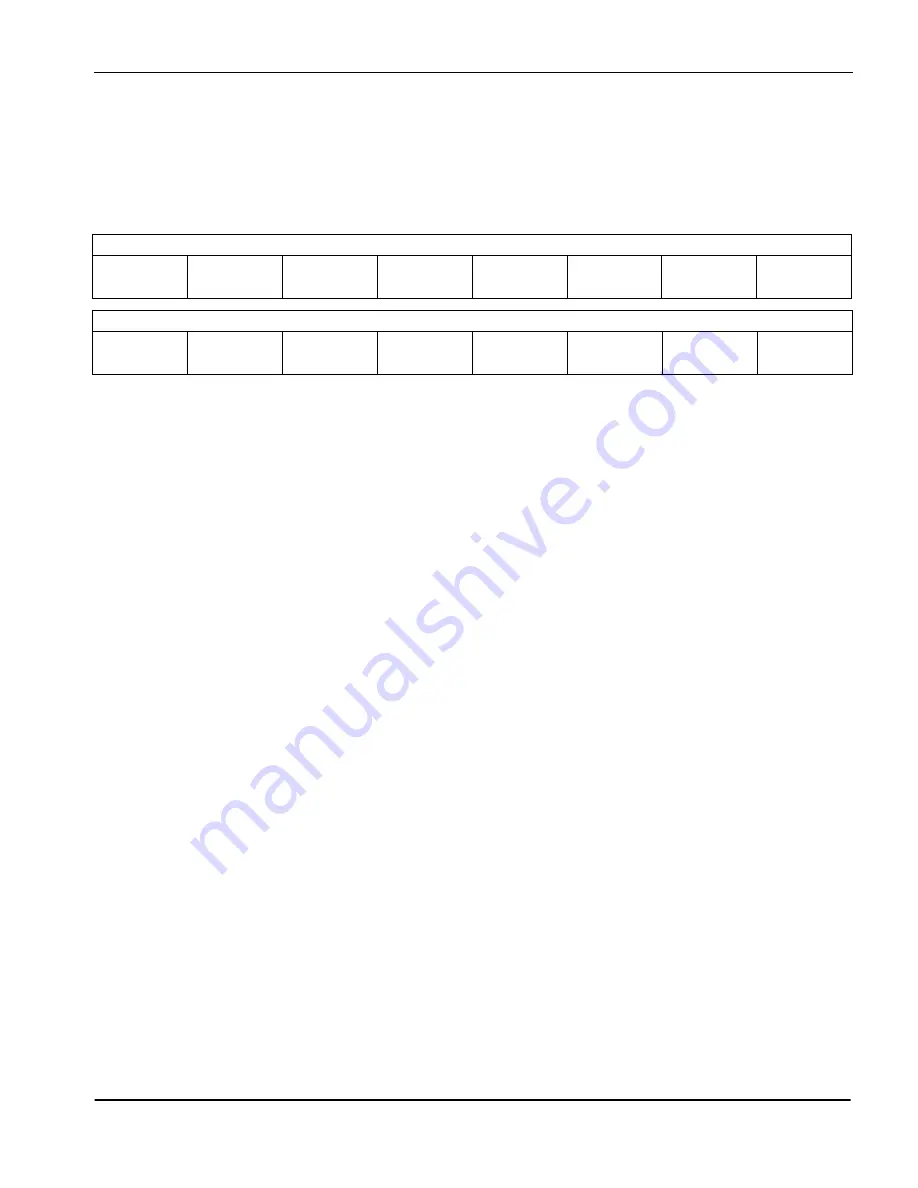

Figure 5-5: Screen 1 Vertical Size

These two registers form a ten bit value which determines the size of screen 1. When the

vertical size is equal to or greater than the physical number of lines being displayed there

is no visible effect on the display. When the vertical size value is less than the number of

physically displayed lines, display operation works like this:

1. From the end of vertical non-display (beginning of a frame) to the number of lines in-

dicated by vertical size the display data will come from the memory pointed to by the

Screen 1 Display Start Address.

2. After vertical size lines have been displayed the system will begin displaying data

from Screen 2 Display Start Address memory.

Screen 1 memory is always displayed at the top of the screen followed by screen 2 memory.

The start address for the screen 2 image may be lower in memory than that of screen 1 (i.e.

screen 2 could be coming from offset 0 in the display buffer while screen 1 was coming

from an offset located several thousand bytes into the display buffer). While not particu-

larly useful, it is even possible to set screen 1 and screen 2 to the same address.

REG[13] Screen 1 Vertical Size (LSB)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

REG[14] Screen 1 Vertical Size (MSB)

n/a

n/a

n/a

n/a

n/a

n/a

Bit 9

Bit 8

*