Epson Research and Development

Page 11

Vancouver Design Center

Interfacing to an 8-bit Processor

S1D13704

Issue Date: 01/02/12

X26A-G-013-02

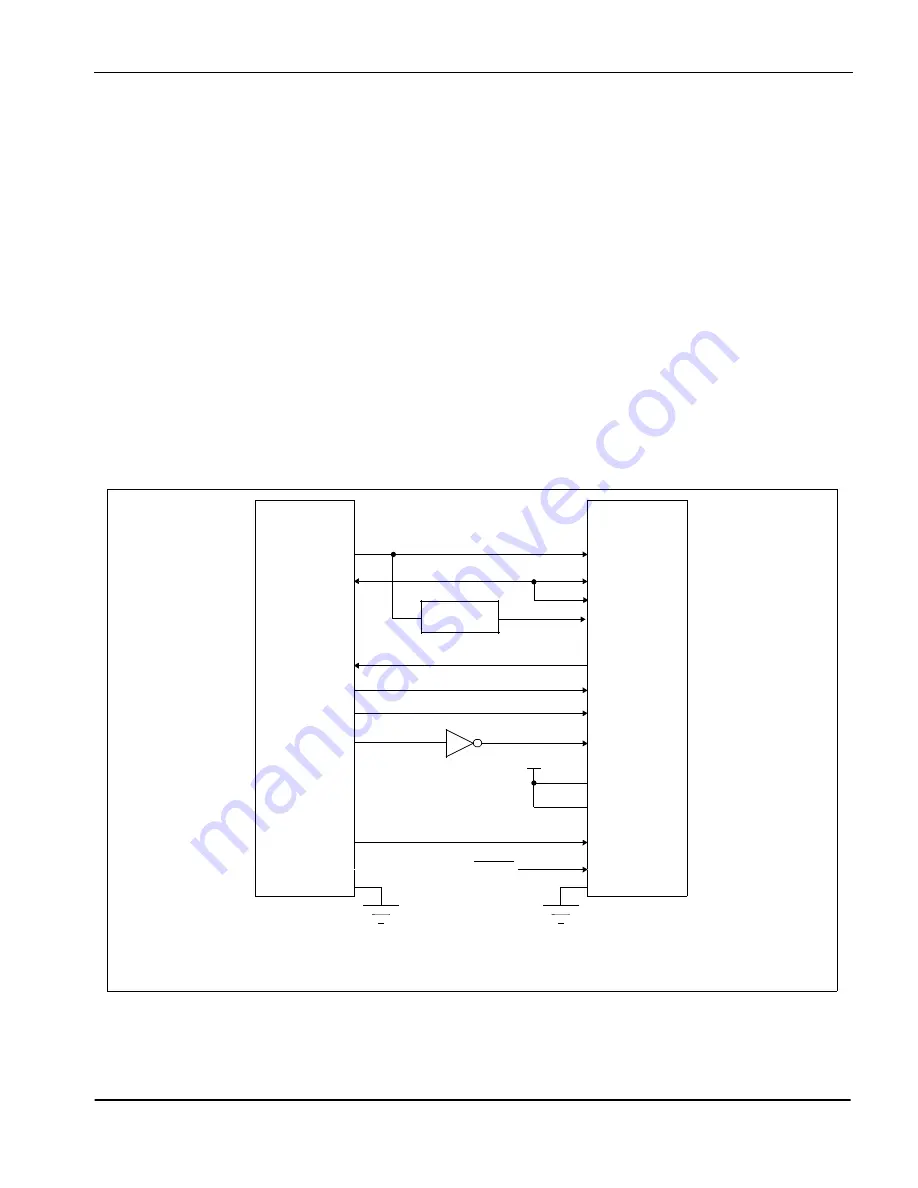

4 8-Bit Processor to S1D13704 Interface

4.1 Hardware Description

The interface between the S1D13704 and an 8-bit processor requires minimal glue logic. A

decoder is used to generate the chip select for the S1D13704 based on where the S1D13704

is mapped into memory. Alternatively, if the processor supports a chip select module, it can

be programmed to generate a chip select for the S1D13704 without the need of an address

decoder.

An inverter inverts A0 to generate the Byte High Enable signal for the S1D13704. If the

8-bit host interface has an active high WAIT signal, it must be inverted as well.

In order to support an 8-bit microprocessor with a 16-bit peripheral, the low and high order

bytes of the data bus must be connected together. The following diagram shows a typical

implementation of an 8-bit processor to S1D13704 interface.

Figure 4-1: Typical Implementation of an 8-bit Processor to the S1D13704 Generic #2 Interface

Generic 8-bit Bus

S1D13704

A[15:0]

D[7:0]

Decoder

WAIT#

WE#

RD#

A0

BUSCLK

AB[15:0]

DB[7:0]

CS#

WAIT#

WE0#

RD#

RD/WR#

BUSCLK

RESET#

DB[15:8]

IO V

DD

BS#

BHE# (WE1#)

System RESET

Note:

When connecting the S1D13704 RESET# pin, the system designer should be aware of all

conditions that may reset the S1D13704 (e.g. CPU reset can be asserted during wake-up

from power-down modes, or during debug states).

*