Epson Research and Development

Page 69

Vancouver Design Center

Hardware Functional Specification

S1D13704

Issue Date: 01/02/08

X26A-A-001-04

bits 7-0

Line Byte Count Bits [7:0]

This register is the byte count from the beginning of one line to the beginning of the next

consecutive line (commonly called “stride” by programmers). This register may be used to

create a virtual image in SwivelView mode.

REG[1Eh] and REG[1Fh]

REG[1Eh] and REG[1Fh] are reserved for factory S1D13704 testing and should not be

written. Any value written to these registers may result in damage to the S1D13704 and/or

any panel connected to the S1D13704.

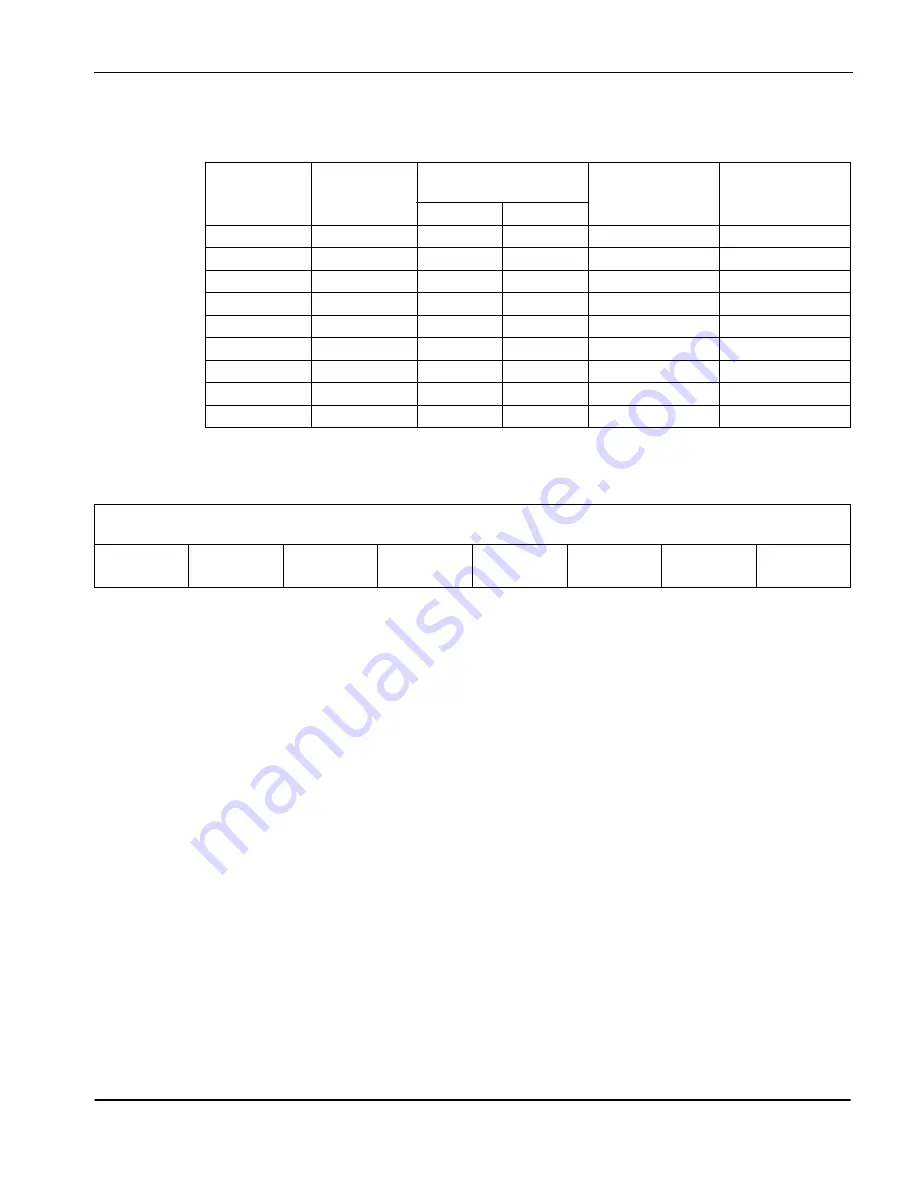

Table 8-9: Selection of PCLK and MCLK in SwivelView Mode

SwivelView

Mode Enable

(REG[1Bh] bit 7)

SwivelView

Mode Select

(REG[1Bh] bit 6)

Pixel Clock (PCLK) Select

(REG[1Bh] bits [1:0]

PCLK =

MCLK =

Bit 1

Bit 0

0

X

X

X

CLK

See Reg[02h] bit 5

1

0

0

0

CLK

CLK

1

0

0

1

CLK/2

CLK/2

1

0

1

0

CLK/4

CLK/4

1

0

1

1

CLK/8

CLK/8

1

1

0

0

CLK/2

CLK

1

1

0

1

CLK/2

CLK

1

1

1

0

CLK/4

CLK/2

1

1

1

1

CLK/8

CLK/4

Where CLK is CLKI (REG[02h] bit 4 = 0) or CLKI/2 (REG[02h] bit 4 = 1)

REG[1Ch] Line Byte Count Register for SwivelView Mode

Address = FFFCh

Read/Write

Line Byte

Count bit 7

Line Byte

Count bit 6

Line Byte

Count bit 5

Line Byte

Count bit 4

Line Byte

Count bit 3

Line Byte

Count bit 2

Line Byte

Count bit

1

Line Byte

Count bit

0

*