7. COMMAND

S1D15722D01B000 Technical Manual (Rev.1.1)

EPSON

31

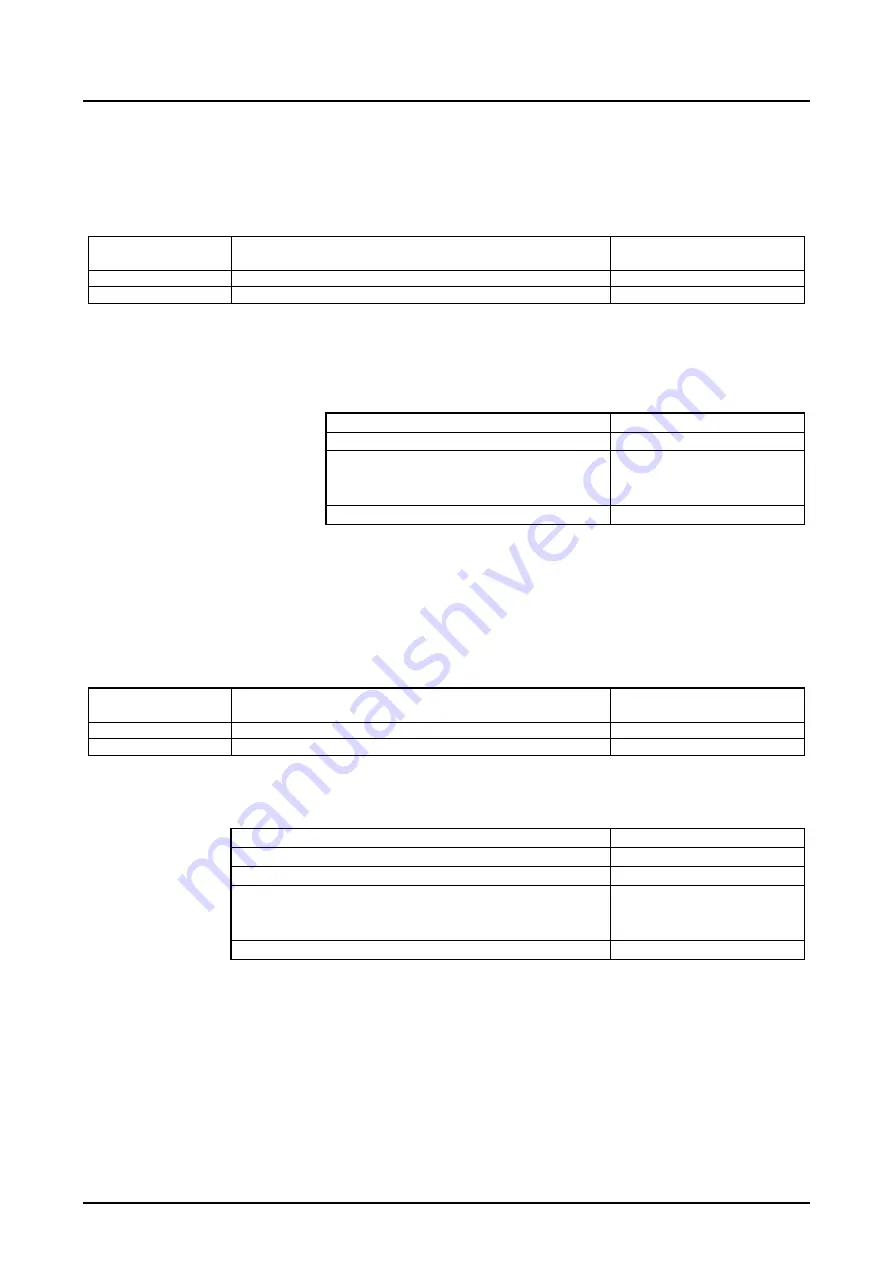

(6) Set page address

This command specifies the page address that corresponds to the row address when making an access to the

display data RAM shown in Figs.6.5 and 6.6 from the side of MPU.

For more information, see 6.2.3 Page Address Circuit/Column Address Circuit in FUNCTIONAL

DESCRIPTION.

E R/

__

W

A0

___

RD

___

WR D7 D6 D5 D4 D3 D2 D1 D0

Command

0 1 0 1 0 1 1 0 0 0 1

Set

mode

1 1 0

*

*

P5 P4 P3 P2 P1 P0

Set

register

Note: An asterisk (*) denotes invalid bit.

Relationship between the register value with set register and page address is shown below.

P5 P4 P3 P2 P1 P0

Page

address

0 0 0 0 0 0

00H

(Page

0)

0 1 0 0 1 1

01H

(Page

1)

↓

↓

1 0 1 1 0 0

2CH

(Page

44)

1 0 1 1 0 1

2DH

(Page

45)

Note: After resetting by the

____

RES pin, the address is set to 00H.

Note: Register setting at (1, 0, 1, 1, 1, 0) or higher is not allowed.

(7) Set column address

This command specifies the column address of the display data RAM shown in Figs.6.5 and 6.6. For more

information, see 6.2.3 Page Address Circuit/Column Address Circuit in FUNCTIONAL DESCRIPTION.

E R/

__

W

A0

___

RD

___

WR D7 D6 D5 D4 D3 D2 D1 D0

Command

0 1 0 0 0 0 1 0 0 1 1

Set

mode

1 1 0 P7 P6 P5 P4 P3 P2 P1 P0

Set

register

Relationship between the register value with the set register and column address is shown below.

P7 P6 P5 P4 P3 P2 P1 P0

Column

address

0 0 0 0 0 0 0 0

00H

0 0 0 0 0 0 0 1

01H

0 0 0 0 0 0 1 0

02H

↓

↓

1 1 0 1 1 1 1 0

DEH

1 1 0 1 1 1 1 1

DFH

Note: After resetting by the

____

RES pin, the address is set to the column 00H.

Note: Register setting at (1, 1, 1, 0, 0, 0, 0, 0) or higher is not allowed.