S1R72104 Technical Manual

Rev.1.1

EPSON

5

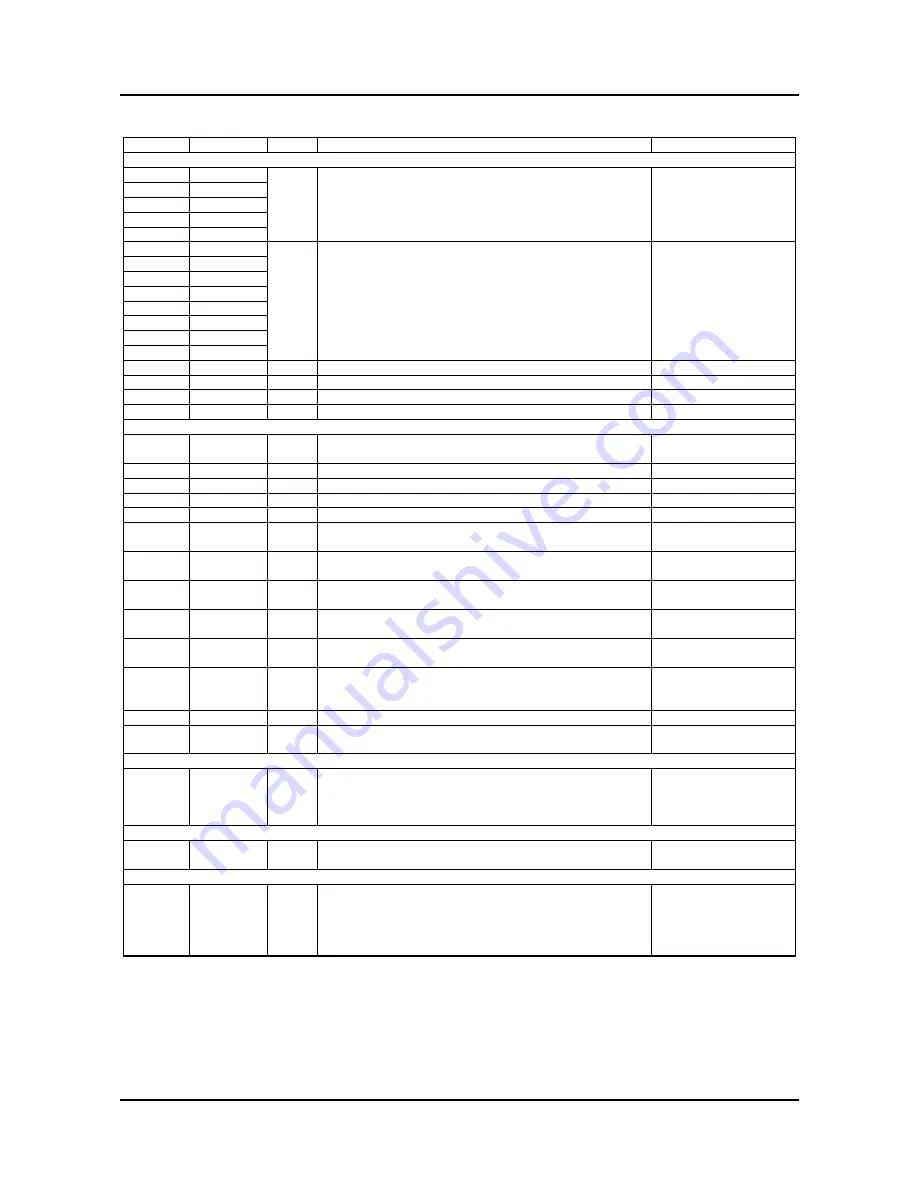

Pin No.

Symbol

I/O

Functional description

Remarks

CPU interface-related matters (17)

24

AD0

Ipu

Address input pin (AD0 to AD4)

27 AD1

28 AD2

29 AD3

30 AD4

15

DB0

Ipu/O Data pin (DB0 to DB7)

Drive capability 3mA

16 DB1

17 DB2

18 DB3

20 DB4

21 DB5

22 DB6

23 DB7

35

XCS

Ispu Chip select signal for accessing internal register

34

XINT

Otr

Interrupt request output signal

Drive capability 6mA

32

XRD

Ispu Data lead signal

31

XWR

Ispu Data write signal

Others (17)

4

OSCIN

I

Input to built-in oscillation circuit (40MHz, 20MHz or

22.5MHz)

5

OSCOUT

O

Output from built-in oscillation circuit

13

TESTMON

O

Monitor output for testing (open “LOW” output usually)

Drive capability 2mA

33

XRESET

Ipu

System reset input signal

14

TESTEN

Ipd

Pin for testing (connected to LOW (GND) usually)

7

CLKSEL0

I

Input clock selection: LOW(GND): OSCIN / HIGH(LV

DD

):

EXCLK input

8

CLKSEL1

I

System clock selection: LOW(GND): PLL output /

HIGH(LV

DD

): Selecting signal of CLKSEL0

11

PLLCT0

I

Dependent on PLL operation control pin input clock; input

on 3.3V level

12

PLLCT1

I

Dependent on PLL operation control pin input clock; input

on 3.3V level

2

EXCLK

I

5V level external clock input pin (connected to LOW (GND)

when not used)

10

XPLLPD

I

PLL power-down pin

LOW (GND): PLL Power-down mode / HIGH (LV

DD

): PLL

operation

9 V

C

O

Internal

V

CO

control pin

74,83,

93,99

NC

- Not connected to IC chips (open usually)

HV

DD

:5V (5)

19,45,62,

72,76,80,

85,89,94,

98

HV

DD

P

Power supply for 5V interface

LV

DD

:3.3V (6)

1,6,26,51

LV

DD

P

Power supply for internal operation

V

SS

:0V (17)

3,25,36,

50,60,64,

67,70,75,

78,82,87,

91,96,100

V

SS

P

GND

Note :

I

: Input

O

: Output

Is

: Schmitt input

Ood

: Open drain output

Ipu

: Pull-up input

Otr

: Tristate output

Ispu

: Pull-up Schmitt input

Ipd

: Pull-down input