S1R72104 Technical Manual

Rev.1.1

EPSON

41

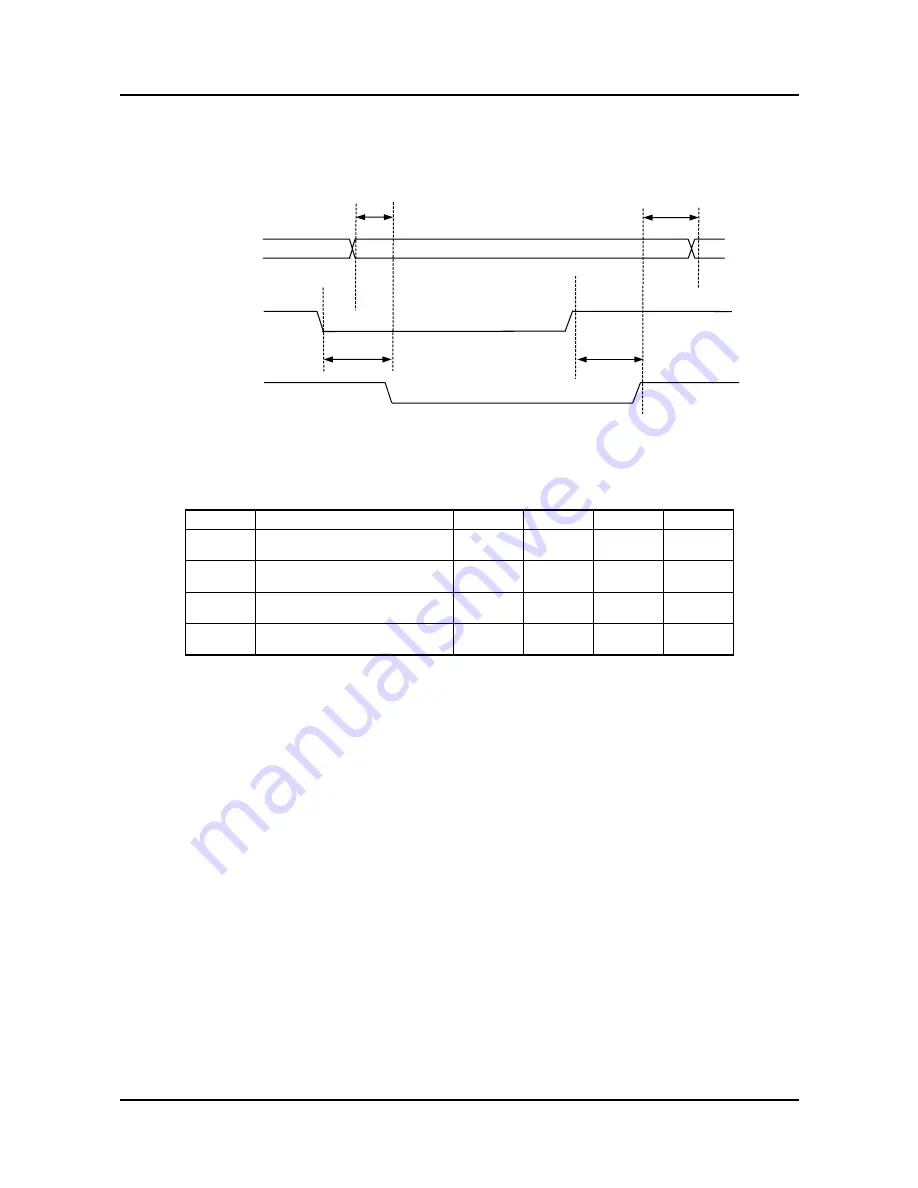

8.4.2.6 Initiator Asynchronous Data-out Timing (Data output)

Symbol Specification Min.

Typ.

Max.

Unit

T

223

XSREQ

↓

-XSACK

↓

25

-

- ns

T

224

XSDB valid –XSACK

↓

100

- - ns

T

225

XSREQ

↑

-XSACK

↑

25

-

90

ns

T

226

XSACK

↑

-XSDB invalid

50

-

- ns

XSDB0-7,P

XSACK

XSREQ

T

224

T

223

T

225

T

226