S1R72104 Technical Manual

Rev.1.1

EPSON

51

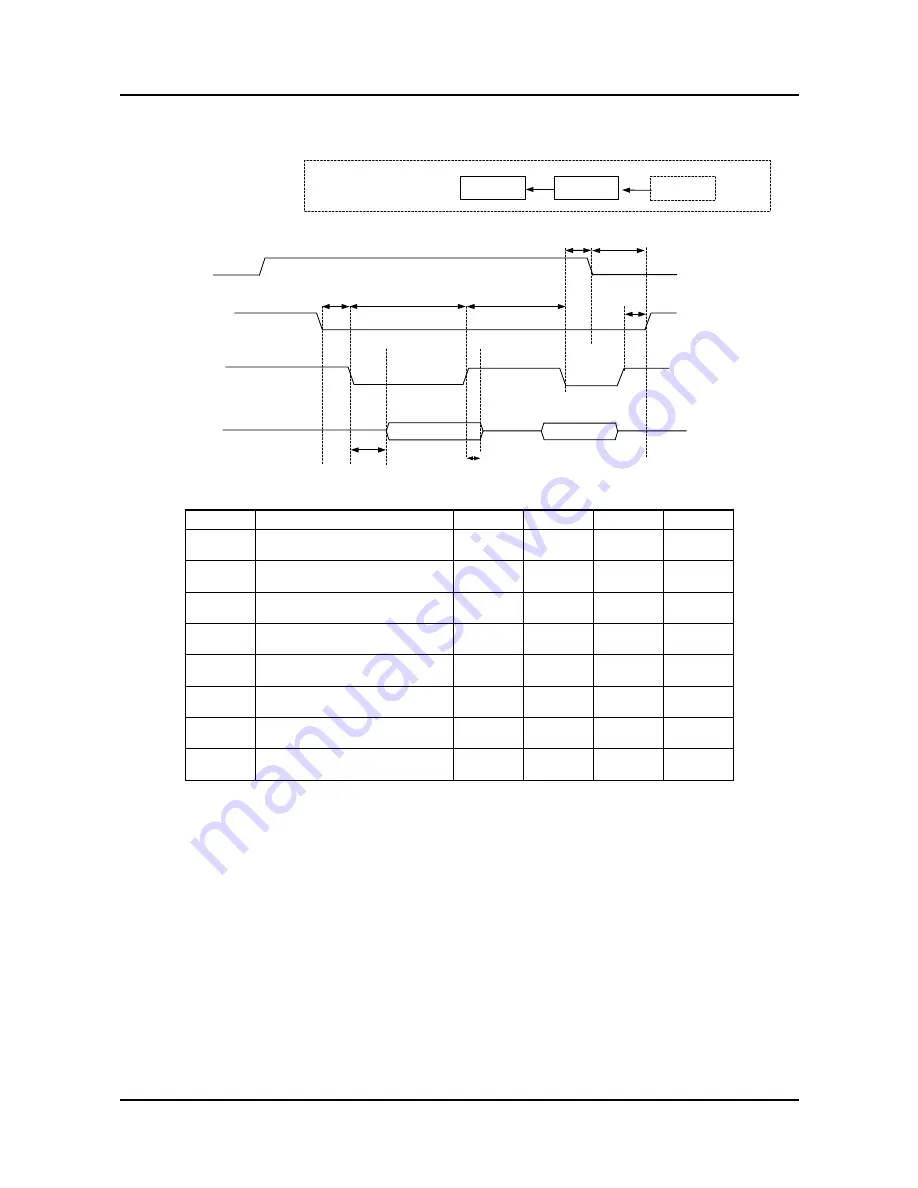

8.4.3.3 DMA Write (PSLV=0: Master mode)

Symbol Specification Min.

Typ.

Max.

Unit

T

333

XPWR

↓

→

PDREQ negate

PDREQ negate delay time

0

- 30 ns

T

334

XPDACK

↓

→

XPWR

↓

XPWR setup time

0

-

5

ns

T

335

XPWR

↓

→

XPWR

↑

XPWR assert pulse width

- (AP+2)

×

25 -

ns

T

336

XPWR

↑

→

XPWR

↓

XPWR negate pulse width

- (NP+2)

×

25 -

ns

T

337

XPWR

↑

→

XPDACK

↑

XPWR hold time

0

-

5

ns

T

338

XPWR

↓

→

PD

Data output delay time Note 1

0

-

25

ns

T

339

XPWR

↑

→

PD(Hi-Z)

Data bus negate time Note 1

5

-

40

ns

T

33A

PDREQ negate

→

XPDACK

↑

XPDACK setup time

5

-

- ns

Note 1: Data is output to PD only while both XPDACK and XPWR are asserted.

PD is always in Input mode except such time.

Direction of data transfer

Prosessor

S1R72104

HOST

PDREQ(I)

XPDACK(0)

XPWR(0)

PD15-0(0)

T

334

T

337

T

336

T

333

T

33A

T

335

T

338

T

339