4. CPUIF Verification Procedure

S1R72V17 CPU Connection Guide

EPSON 11

(Rev. 1.0)

1) Recovery processing from CPU_Cut state

Dummy read the PM_Control register (0x012h address).

The S1R72V17 switches to CPU_Cut state after resetting has been cancelled. This dummy read

operation ends the CPU_Cut state and switches to Sleep. In the Sleep state, reading/writing is possible

to/from all asynchronous registers.

2) Endian setting initialization

Dummy read the CPU_ChgEndian register (0x077h address).

Setting the ChipReset register (0x011h address) AllReset bit to “1” enables the reset CPU_Config

register CPU_Endian setting after this register has been dummy read when the S1R72V17 has been

reset.

3) CPU operating mode setting

Write the usage mode settings to the CPU_Config register CPU_Endian, BusMode, and Bus8x16 bits.

Little-endian CPU: 0x74h address

Big-endian CPU:

0x75h address

This register address is assigned to the 0x075h address. Since the S1R72V17 operates in the default

big-endian state until this setting is changed, the 0x074h address should be accessed to access a

little-endian CPU.

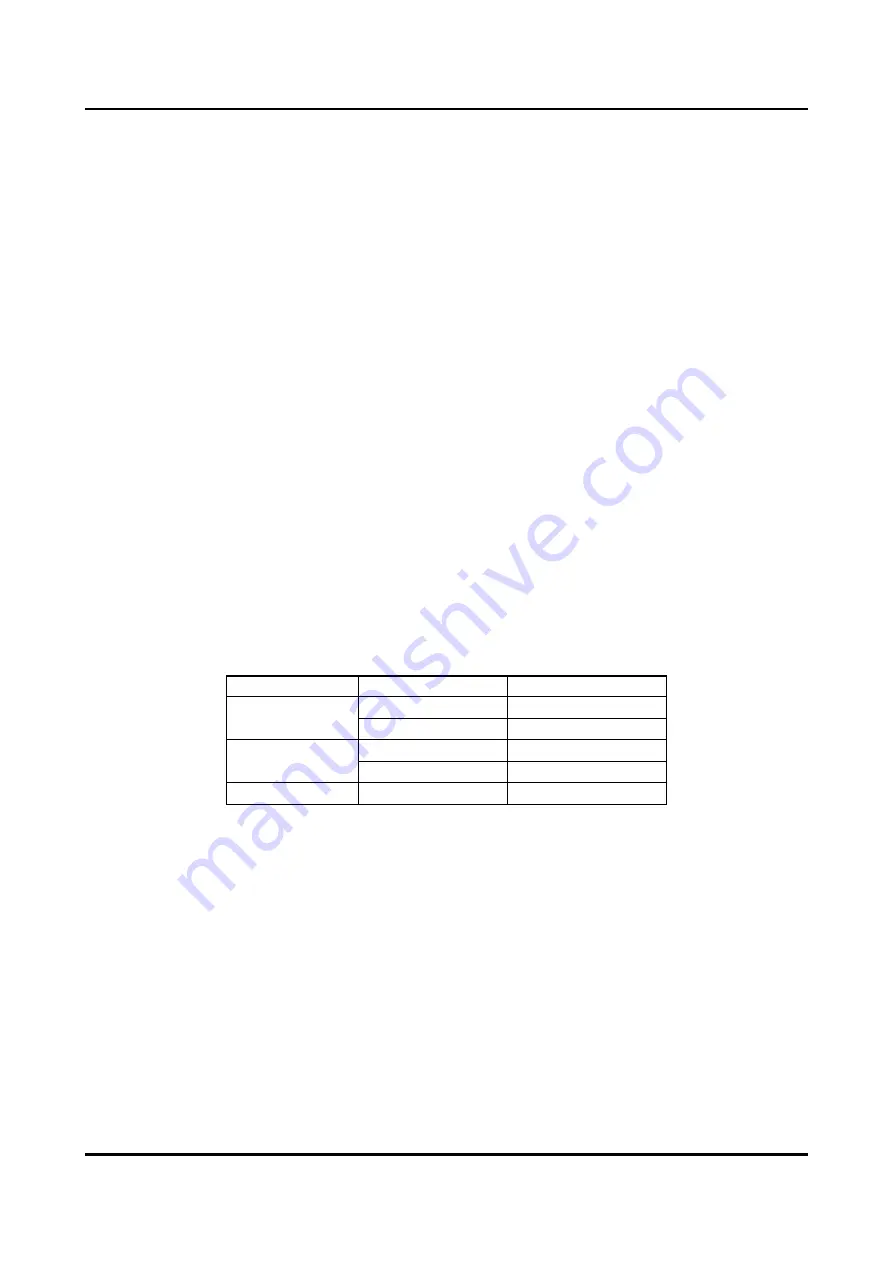

Table 4-1 CPU_Config register settings

Bus mode

CPU endian

Setting

Little Endian

0x04

16-bit Strobe mode

Big Endian

0x00

Little Endian

0x06

16-bit BE mode

Big Endian

0x02

8-bit mode

-

0x01

4) Endian setting enabling

Dummy read the CPU_ChgEndian register (0x77h address).

Reading this register enables the CPU_Endian bit set in 3).

5) Asynchronous

register

access test (Word register)

Read/write test to/from the WakeupTim_L,H registers (0x014 address).

This register can be read/written in the Sleep state. All bits are enabled.

Read/write testing this register checks whether the CPU data bus is correctly connected. If this

read/write operation is not performed correctly, check the physical connection with the CPU.