S1R72803F00A

108

EPSON

C48

0.1u

HV

DD

D[0:15] (2H5)

(2H2) A[1:18]

29

31

33

35

38

40

42

44

30

32

34

36

39

41

43

45

9

10

13

14

16

15

37

46

27

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D55/A-1

NC

NC

NC

NC

NC

RY/BY

V

CC

GND

GND

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

CE

RESET

BYTE

OE

OE

U4

25

24

23

22

21

20

19

18

8

7

6

5

4

3

2

1

48

17

29

29

29

29

29

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

7

8

9

10

13

14

15

16

29

30

31

32

35

36

37

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

V

CC

V

CC

V

SS

V

SS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

xUB

xLB

xCS

xWE

xOE

U3

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

D0

D1

D2

D3

D4

D5

D6

D7

D9

D10

D11

D12

D13

D14

D15

38

11

33

12

34

5

4

3

2

1

44

43

42

27

26

25

24

21

20

19

18

40

39

6

17

41

D15

XRESET

(2G1)

MBM29F400TC-70PFTN

TC551664BFT

HV

DD

HV

DD

C49

0.1u

HV

DD

HV

DD

XRD

(2H4)

XWRL

(2H4)

XCE10EX

JUMP-3

JP4

10K

R66

10K

R67

2

1

3

(2D5)

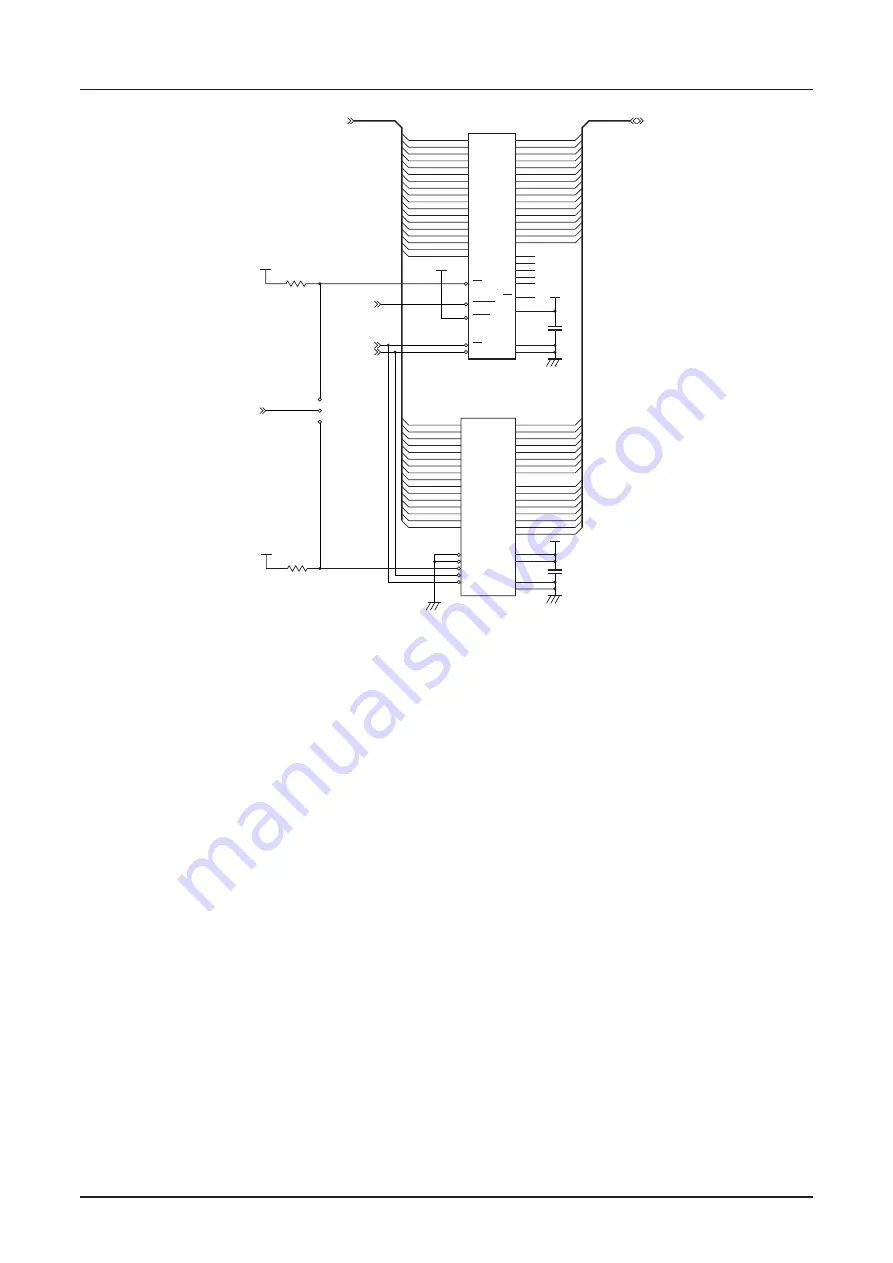

Note: The circuit of this sheet is an example of connection when an external ROM and SRAM are connected during

the process of system development. This circuit is not required on a system of finished product.