S1R72803F00A

18

EPSON

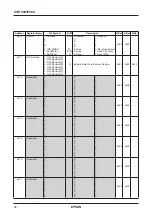

7.6 FLASH CONTROLLER

This IC is provided with a function to perform Erase and

Write to the Flash ROM.

(1) Chip Erase

According to a specified sequence, you can erase all

memory cells in the built-in Flash ROM to put them

in “1” status.

After erasing the chip, check that the data of all

memory cells is “1”.

(2) Sector Erase

This IC is ready for the Sector Erase in the unit of

512 words/sector.

According to a specified sequence, you can erase all

memory cells in the built-in Flash ROM to put them

in “1” status.

After erasing the chip, check that the data of all

memory cells is “1”.

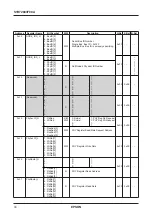

(3) Write

Write is complete if you continue writing Write data

in the unit of word until writing of all sectors (512

words) finishes.

On completion of the Sector Write, compare all data

in the sectors with original data for confirmation.

You cannot change the data of the memory cell from

“0” to “1” by writing.