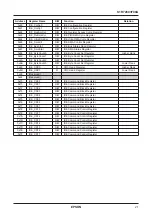

S1R72803F00A

EPSON

19

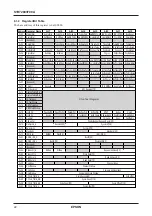

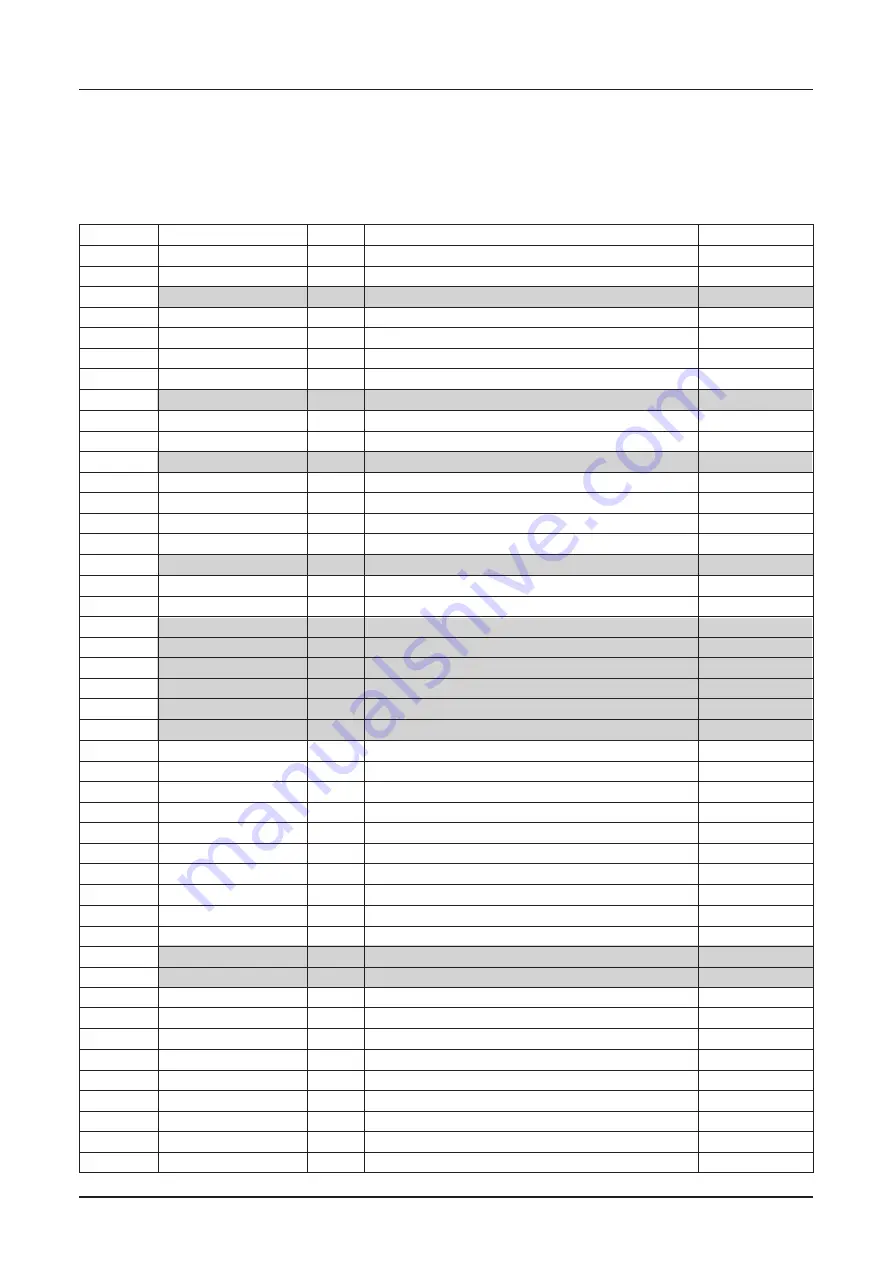

8. INTERNAL REGISTER

8.1 IEEE1394 LINK CONTROLLER REGISTER MAPPING

8.1.1

Register Table

(The base address of this register is 0x100000.)

Address

Register Name

R/W

Function

Relation

0x00

MainIntStat

R(W)

Main Interrupt Status Register

0x01

SubIntStat

R(W)

Sub-Interrupt Status Register

0x02

(Reserved)

0x03

DmaIntStat

R(W)

DMA Interrupt Status Register

0x04

LinkIntStat1

R(W)

LINK Core Interrupt Status Register 1

0x05

LinkIntStat0

R(W)

LINK Core Interrupt Status Register 0

0x06

PhyIntStat

R(W)

PHY Interrupt Status Register

0x07

(Reserved)

0x08

MainIntEnb

R/W

Main Interrupt Enable Flag Register

0x09

SubIntEnb

R/W

Sub-Interrupt Enable Flag Register

0x0A

(Reserved)

0x0B

DmaIntEnb

R/W

DMA Interrupt Enable Flag Register

0x0C

LinkIntEnb1

R/W

LINK Core Interrupt Enable Flag Register 1

0x0D

LinkIntEnb0

R/W

LINK Core Interrupt Enable Flag Register 0

0x0E

PhyIntEnb

R/W

PHY Interrupt Enable Flag Register

0x0F

(Reserved)

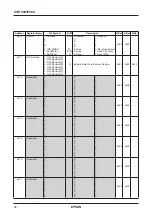

0x10

ChipCtl

R/W

Chip Control Register

0x11

HW_Revision

R/W

Hardware Revision Register

0x12

(Reserved)

0x13

(Reserved)

0x14

(Reserved)

0x15

(Reserved)

0x16

(Reserved)

0x17

(Reserved)

0x18

LinkCtl_H

R/W

LINK Core Control Register

Higher Rank

0x19

LinkCtl_L

R/W

LINK Core Control Register

Lower Rank

0x1A

LinkStat

R

LINK Core Status Read Register

0x1B

PriReqCnt

R

Priority Request Count Register

0x1C

RetryLimit_H

R/W

Dual Retry Time Set Register

Higher Rank

0x1D

RetryLimit_L

R/W

Dual Retry Time Set Register

Lower Rank

0x1E

MaxRetry

R/W

Single Retry Number Set Register

0x1F

IRM_Stat

R/W

IRM Status Register

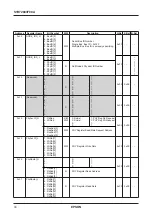

0x20

NODE_IDS_H

R/W

Node IDS Status Register

Higher Rank

0x21

NODE_IDS_L

R/W

Node IDS Status Register

Lower Rank

0x22

(Reserved)

0x23

(Reserved)

0x24

PhyAccCtl_H

R/W

LINK Core Control Register

Middle Rank

0x25

PhyAccCtl_L

R/W

LINK Core Control Register

Lower Rank

0x26

PhyRdstat_H

R

LINK Core Status Read Register

0x27

PhyRdstat_L

R/W

Priority Request Count Register

0x28

ChnlIndex

R/W

ISO Async Stream Channel Index Register

0x29

ChnlWindow

R/W

ISO Async Stream Channel Window Register

0x2A

CmprIndex

R/W

Compare Offset Address Index Register

0x2B

CmpRW indow

R/W

Compare Offset Address Window Register

0x2C

CYCLE_TIME_H

R/W

Cycle Time Register

Higher Rank