S1R72803F00A

42

EPSON

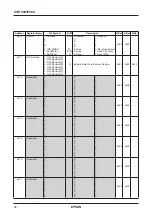

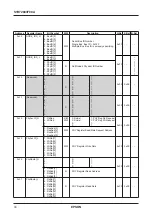

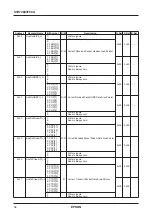

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x00

MainIntStat

7:SubIntStat

R(W)

0: None

1: Sub Interrupt Occurred

6: TxIsoCmp

R(W)

0: None

1: ISO Pkt Transmit Done

5: RxDmaCmp

R(W)

0: None

1: Packet Reception

4: TxAsyCmp

R(W)

0: None

1: AckCode Reception

0x00

0x00

–

3: HwSBP2Cmp R(W)

0: None

1: HwSBP2 Process Complete

2: IDE_DmaCmp R(W)

0: None

1: IDE DMA Transmit Complete

1: IDE_INTRQ

R(W)

0: None

1: IDE Interface Interrupt

0: BusReset

R(W)

0: None

1: Bas Reset Detected

8.1.4 Detail Description of Register

(The base address of this register is 0x100000.)

Main Interrupt Status Register

When this IC interrupts the CPU, the CPU first reads this register to handle it, indicating which Interrupt Status

Register is a factor of this interrupt.

Subsequent to reading this register, the SubIntStat (Bit 7) reads an Interrupt Status Register associated with each

bit to confirm which bit is an interrupt source and appropriately handle it. After that, it writes the read value

to the Interrupt Status Register to clear the bit. In the case the interrupt factor still remains, however, the bit is

not cleared.

When one of 7 bits of the TxIsoCmp, RxDmaCmp, TxAsyCmp, HwSBP2Cmp, IDE_DmaCmp, IDE_INTRQ,

and BusReset other than above is an interrupt source, this register clears the bit by writing the read value.

Note) The bits of this register control the XInt of output pin. Writing to this register negates the XInt once even if the

interrupt factor remains, asserting the XInt after a certain period. (Ready for a timer or edge interrupt).

Bit7 Sub Interrupt Status

When an interrupt factor exists at each bit shown at the SubIntStat Register, this bit becomes “1”.

Bit 6 Isochronous Packet Transmit Complete

When an ISO Packet Transmit is complete, this bit becomes “1”.

Bit5 Receive Packet DMA Complete

When a received packet is written to the Receive Buffer Area, this bit becomes “1”.

Bit4 Asynchronous Packet Transmit Complete

When an Ack packet to an Async Transmit packet is received, this bit becomes “1”.

The Ack code is written to the footer area of the Transmit Packet Header.

Bit 3 HwSBP2 Process Complete

When a HwSBP2 processing is complete, this bit becomes “1”.

Bit2 IDE DMA Transmit Complete

When an IDE I/F DMA Transmit is complete, this bit becomes “1”.

Bit1 IDE Interface Interrupt

When the INTRQ signal is asserted to the IDE I/F, this bit becomes “1”.

Bit0 BusReset Detected

When a BusReset signal is detected on the 1394 Serial Bus, this bit becomes “1”.

When it issues a BusReset, this bit becomes “1” as well.