S1R72803F00A

EPSON

43

Sub-Interrupt Status Register

The value of each bit of this register indicates the status of a corresponding interrupt source. If these bits become

“1” when the associated bit of the SubIntEnb Register is “1”, this register asserts an interrupt signal to the CPU.

The CPU reads this register after receiving the interrupt signal to locate an interrupt source. By writing the read

value again, it clears these bits.

Subsequent to reading this register, the lower order 4 bits reads the Interrupt Status Register associated with each

bit to confirm which bit is an interrupt source and appropriately handle it. After that, it writes the read value

to the Interrupt Status Register to clear the bit. In the case that the interrupt factor still remains, however, the

bit is not cleared.

Bit7 Self Identify Period Complete

When a Self ID period finishes, this bit becomes “1”.

Bit6 Self Identify Packet Error

When a Self-ID packet with an error is received during the Self-ID period or when the Self-ID period finishes

due to an error, this bit becomes “1”.

Bit5 HwSBP2Err

When an interrupt factor from the HwSBP2 indicated on the HwSBP2IntStat Register exists, this bit becomes

“1”.

Bit4 BusReset in process HwSBP2

When a BusReset occurs in the HwSBP2 processing, this bit becomes “1”.

Bit3 LINK Core Interrupt Status1

When an interrupt factor from the LINK core indicated on the LinkIntStat1 Register exists, this bit becomes “1”.

Bit2 LINK Core Interrupt Status0

When an interrupt factor from the LINK core indicated on the LinkIntStat0 Register exists, this bit becomes “1”.

Bit1 PHY/LINK Interrupt Status

When an interrupt factor from the PHY status indicated on the PHYIntStat Register exists, this bit becomes “1”.

Bit0 LINK DMA Interrupt Status

When an interrupt factor exists in the internal DMA operation indicated on the DmaIntStat Register, this bit

becomes “1”.

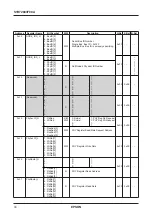

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x01

SubIntStat

7: SelfIDdone

R(W)

0: None

1: Self-ID Phase Done

6: SelfIDerr

R(W)

0: None

1: Self-ID Packet Error

5: HwSBP2Err

R(W)

0: None

1: Hw SBP2 Error

4: HwSBP2BRst R(W)

0: None

1: BusReset in process HwSBP

0x00

0x00

–

3: LinkIntStat1

R(W)

0: None

1: Link1 Interrupt Occurred

2: LinkIntStat0

R(W)

0: None

1: Link0 Interrupt Occurred

1: PhyIntStat

R(W)

0: None

1: PHY Interrupt Occurred

0: DmaIntStat

R(W)

0: None

1: Dma Interrupt Occurred

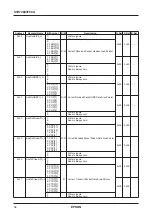

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x02

(Reserved)

7:

0:

1:

6:

0:

1:

5:

0:

1:

4:

0:

1:

0x00

0x00

–

3:

0:

1:

2:

0:

1:

1:

0:

1:

0:

0:

1: