S1R72803F00A

EPSON

45

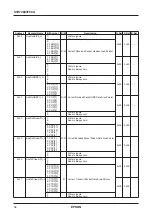

LINK Core Interrupt Status Register 1

The value of each bit of this register indicates the status of a corresponding interrupt source. If these bits become

“1” when the associated bit of the LINKIntEnb1 Register is “1”, this register asserts the interrupt signal to the

CPU.

The CPU reads this register after receiving the interrupt signal to locate an interrupt source. By writing the read

value again, it clears these bits.

Bit7 Reserved

Bit6 Reserved

Bit5 Reserved

Bit4 Reserved

Bit3 RxOnTardy

When a packet is received when the ChipCtl. SendTardy bit is “1”, an Ack_tardy is returned to the party of the

other end and this bit becomes “1”.

Bit2 Receive Packet Header CRC Error

When an error exists in the header CRC of a received packet, this bit becomes “1”.

Bit1 Receive Packet Tcode Unknown

When the Tcode in a received packet is invalid, this bit becomes “1”.

Bit0 transmit Retry Exceeded

If a transmit retry fails since the set value of the MaxRetry Register is exceeded when the RetryLimit Register

is not zero or the MaxRetry Register is not 0 and this bit becomes “1”.

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x04

LinkIntStat1

7:

0:

1:

6:

0:

1:

5:

0:

1:

4:

0:

1:

0x00

0x00

–

3: RxOnTardy

R(W)

0: None

1: Ack_tardy Sent

2: RxHcrcErr

R(W)

0: None

1: Rx Packet Header CRC Err

1: RxUnkTcode

R(W)

0: None

1: Rx Packet Tcode Unknown

0: TxRtyExced

R(W)

0: None

1: Tx Retry Exceeded