S1R72803F00A

EPSON

51

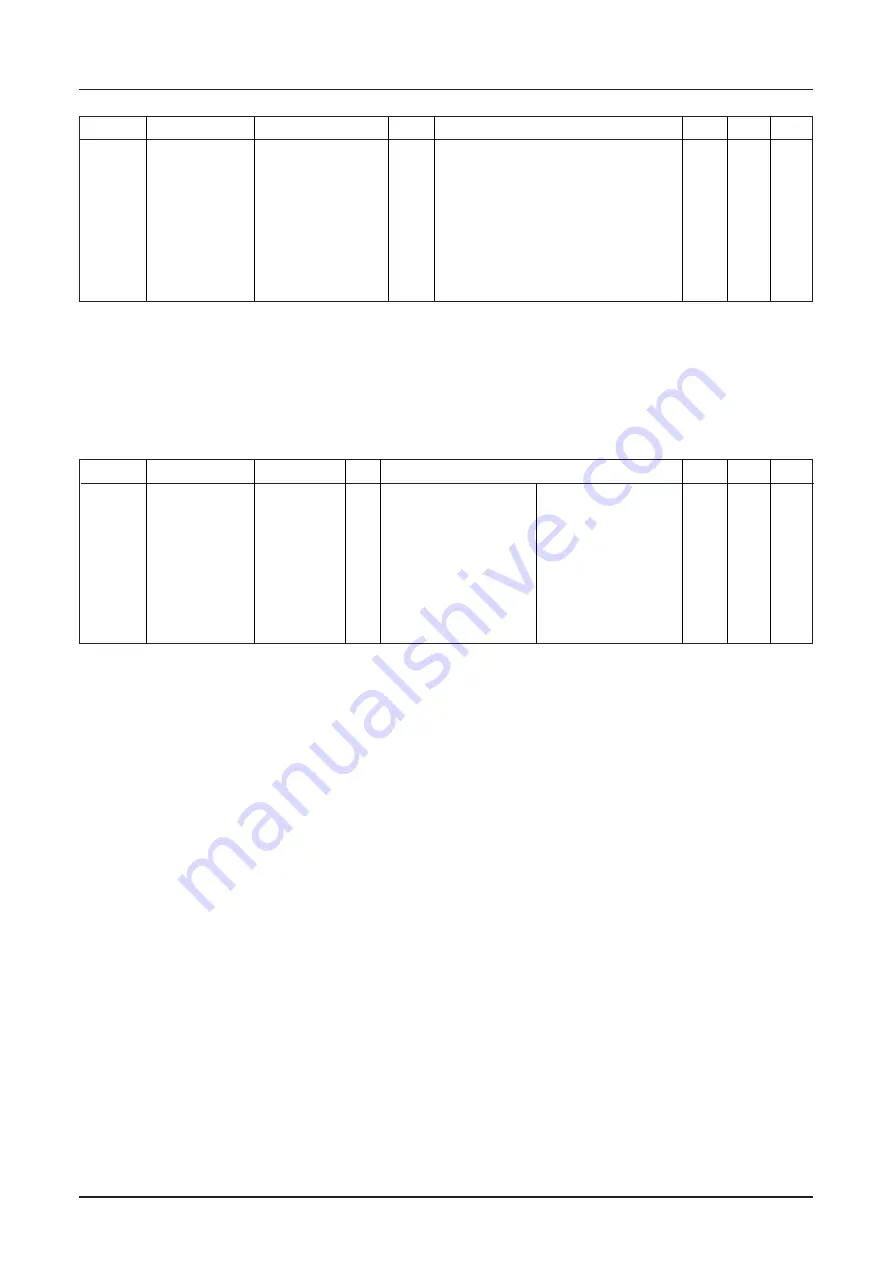

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x11

HW_Revision

7: HW_Revision[7]

6: HW_Revision[6]

5: HW_Revision[5]

4: HW_Revision[4]

R

Indicate Hard Ware Revison Number

0x03

0x03

0x03

3: HW_Revision[3]

2: HW_Revision[2]

1: HW_Revision[1]

0: HW_Revision[0]

Hardware Revision Register

The HW_Revision Register indicates the revision number of a chip.

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x18

LinkCtl_H

7: PassSelfID

0: Non PassSelfID

1: Self–ID to DMA FIFO

6: PassPhyPkt

0: Non Pass PHY Packet

1: PHY Pkt to DMA FIFO

5: PassBrPkt

0: Non Pass BusRst Packet

1: BusRst Pkt to DMA FIFO

4: EnPosWB

R/W 0: Disable Posted WB

1: Enable Posted WB

0x00

0x00

–

3: EnPosWQ

0: Disable Poosted WQ

1: Enable Posted WQ

2: APHY

0: PHY 1394.a uncorrespond 1: PHY 1394.a correspond

1: EnAcc

0: Ack Acceleration Disable 1: Ack Acceleration Enable

0: Cmstr

0: Cycle Master Not Capabl 1: Cycle Master Capable

LINK Core Control Register Higher Rank

This register controls the functions of the LINK core.

Bit7 Pass Self-ID Packet

Setting this bit to “1” captures a Self-ID packet received by the LINK core into the buffer.

Bit6 Pass PHY Packet

When requesting the PHY Register for a register write, this bit is set to “1”. After the execution, this bit is

cleared.

Bit5 Pass BusReset Packet

Setting this bit to “1” captures a BusReset packet received by the LINK core into the buffer.

Bit4 Enable Posted Block Write

Setting this bit to “1” enables the Posted Write function for a Block Write Request.

Bit3 Enable Posted Quadlet Write

Setting this bit to “1” enables the Posted Write function for a Quadlet Write Request.

Bit2 APHY

Indicates whether the PHY conforms to 1394.a or not.

1: Conforms to PHY 1394.a

0: Does not conform to PHY 1394.a

Bit1 Enable Ack Acceleration

Indicates the setting of Ack Acceleration.

1: Ack Acceleration enable

0: Ack Acceleration disable

Bit0 cmstr

When the self node is Cycle Master capable and a root, this bit becomes “1”.

If the self node does not become a root in the Self-ID processing when this bit is set after the Bus Reset, this

bit is cleared.