S1R72803F00A

EPSON

55

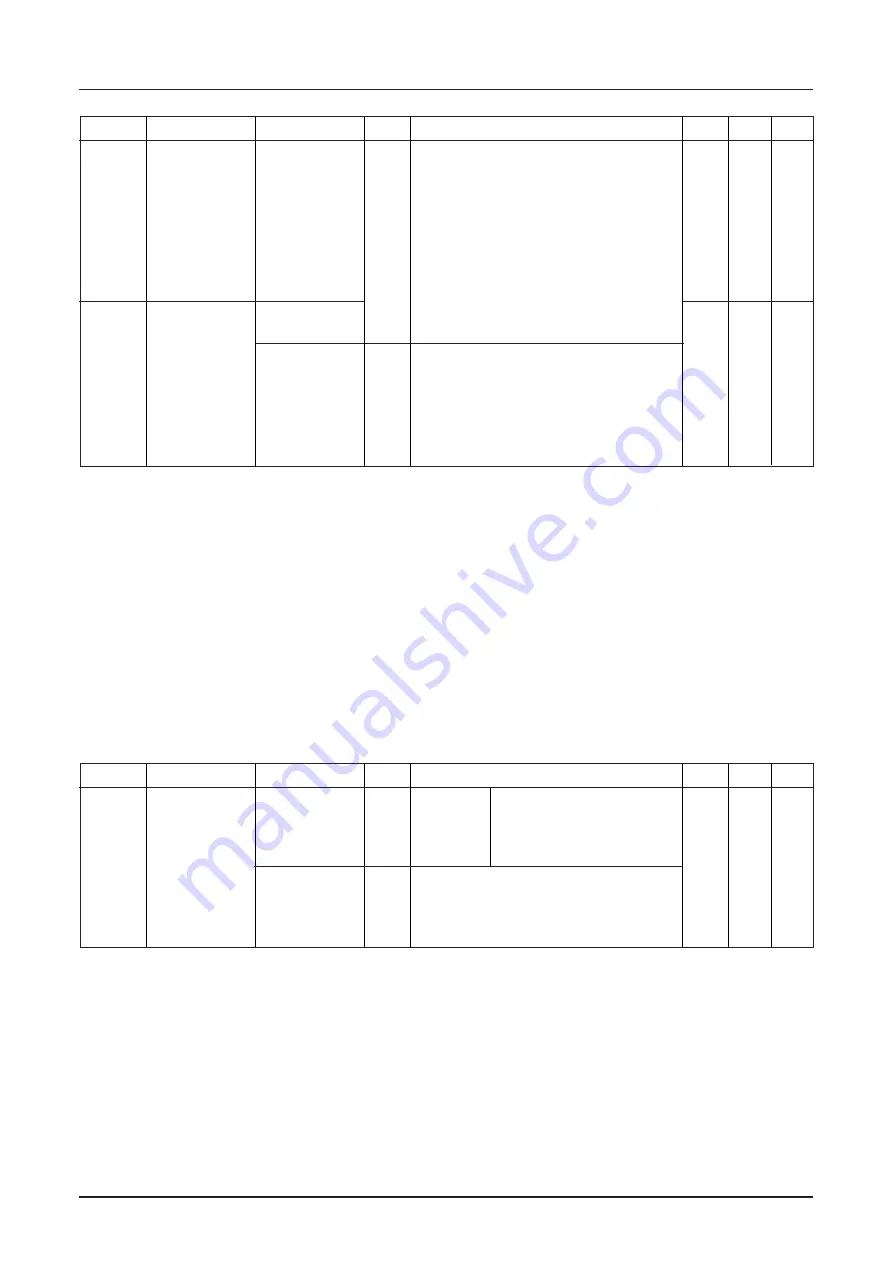

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x20

NODE_IDS_H

7: BusID[9]

6: BusID[8]

5: BusID[7]

Serial Bus ID Number

4: BusID[6]

Single Bus, Bus ID = 0x3FF

0xFF

–

–

3: BusID[5]

R/W

Multiple Bus, Bus ID is uniquely specifying

2: BusID[4]

1: BusID[3]

0: BusID[2]

0x21

NODE_IDS_L

7: BusID[1]

–

6: BusID[0]

–

5: PhyID[5]

1

4: PhyID[4]

0xFF

–

1

3: PhyID[3]

R

Self Node's Physical ID Number

1

2: PhyID[2]

1

1: PhyID[1]

1

0: PhyID[0]

1

Node IDS Status Register (Higher Rank, Lower Rank)

This register indicates the bus ID of topology connected through the serial bus.

At the time of BusReset, the BusID does not change. When the self node is a bus manager, this register is

writable. If you write when it is not a bus manager, the bus goes out of control. Never write when it is not a

bus manager.

The PHY ID becomes a value of the 0x3F at the time of BusReset and is automatically stored on completion

of the Self-ID processing.

0x20, 0x21 .Bit7..6 Bus ID

These bits are areas to store the Bus_ID value of the serial bus.

0x21 Bit5:0 PHY ID

Indicates the Physical ID of a node established by the PHY in the Self-ID phase.

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x24

PhyAccCtl_H

7: RdReq

R/W

0: Normal

1: PHY Reg Rd Request

6: WrReq

R/W

0: Normal

1: PHY Reg Wr Request

5:

0:

1:

4:

0:

1:

0x00

0x00

–

3: ReqAdd[3]

2: ReqAdd[2]

R/W

PHY Register Read/Write Request Address

1: ReqAdd[1]

0: ReqAdd[0]

PHY Register Access Control Register (Higher Rank)

Bit7 PHY Register Read Request

When requesting the PHY Register for a register read, this bit is set to “1”. After the execution, it is automatically

cleared.

Bit6 PHY Register Write Request

When requesting the PHY Register for a register write, this bit is set to “1”. After the execution, it is

automatically cleared.

Bit5 Reserved

Bit4 Reserved

Bit3..0 PHY Access Register

Set a register address to access the PHY Register.