S1R72803F00A

EPSON

59

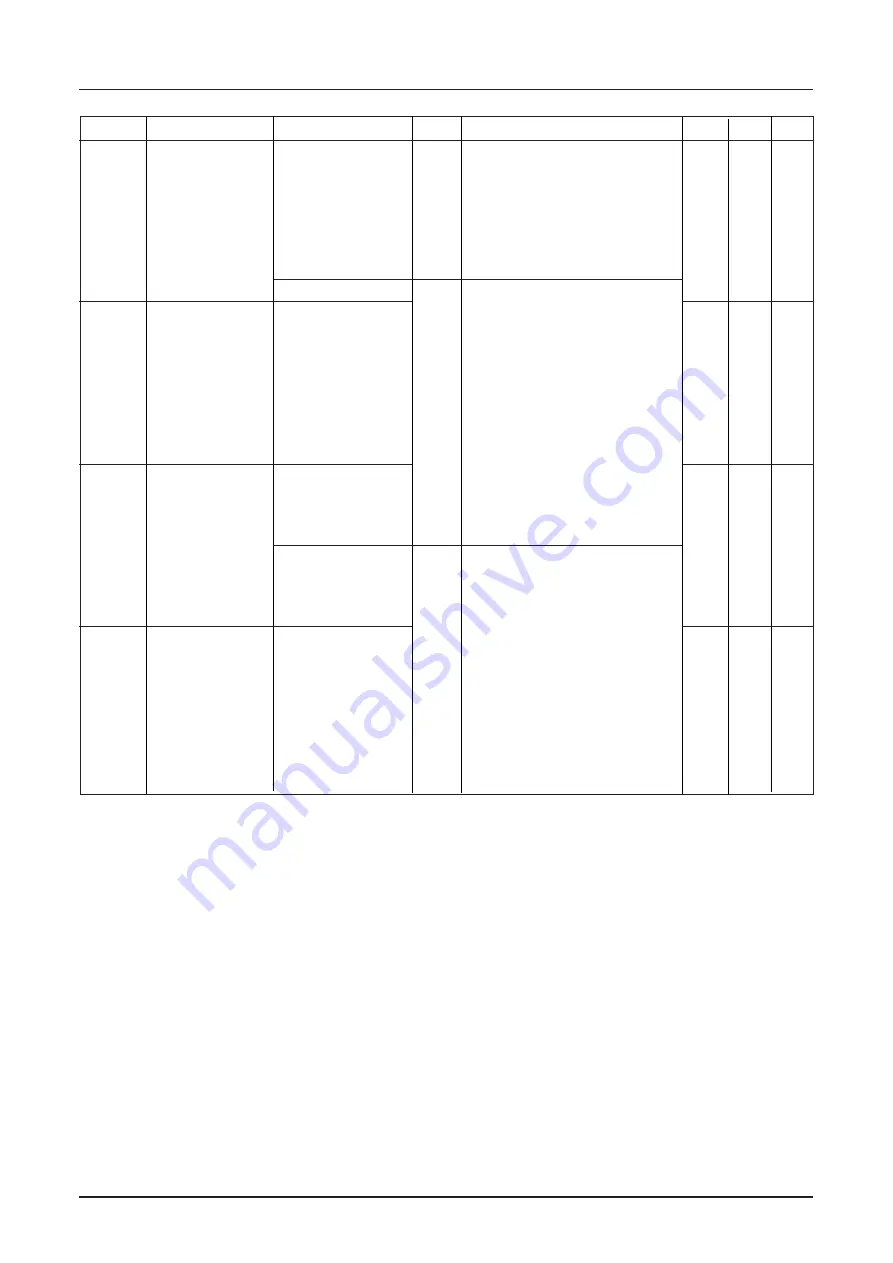

Cycle Time Register

Each of CycSecond, CycCount, and CycOffset Registers updates the timer by updating the current value of the

cycle timer used for isochronous transfer.

When the self node is a CYCLE MASTER, set the value of each register in the CYCLE START PACKET.

When the self node is not a CYCLE MASTER, set the cycle_time_data of a received CYCLE START PACKET

on each register.

This register is enabled when LINKCtl(Hi). DisCycTimer=“0”.

Reserve this register as a CycSecond(Hi) for WORD access.

CYCLE_TIME.second_count

This bit field indicates an integer at the place of Second of the cycle timer.

It is enabled when the LINKCtl(H).DisCycTimer= “0” and the Cycle Second is incremented every time the

CycleCount reaches 8000. When the Cycle Second exceeds 127, it is restored to 0.

CYCLE_TIME.cycle_count

When the self node is a CYCLE MASTER and the DisCycTimer=“0”, it is incremented every time the Cycle

Offset reached 3072. When the Cycle Count reaches 8000, it is restored to 0.

CYCLE_TIME. cycle.offset

When the self node is a CYCLE TIMER and the DisCycTimer=“0”, it is incremented in a cycle of 24.576MHz.

When the Cycle Offset reaches 3072, it is restored to 0 and then the Cycle Count is incremented.

Address

Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x2C

CYCLE_TIME_H

7: Cycle Second[6]

6: Cycle Second[5]

5: Cycle Second[4]

4: Cycle Second[3]

R/W

CYCLE_TIME.second_count

0x00

–

–

3: Cycle Second[2]

2: Cycle Second[1]

1: Cycle Second[0]

0: Cycle Count[12]

0x2D

CYCLE_TIME_MH

7: Cycle Count[11]

6: Cycle Count[10]

5: Cycle Count[9]

4: Cycle Count[8]

0x00

–

–

3: Cycle Count[7]

2: Cycle Count[6]

R/W

CYCLE_TIME.cycle_count

1: Cycle Count[5]

0: Cycle Count[4]

0x2E

CYCLE_TIME_ML

7: Cycle Count[3]

6: Cycle Count[2]

5: Cycle Count[1]

4: Cycle Count[0]

0x00

–

–

3: Cycle Offset[11]

2: Cycle Offset[10]

1: Cycle Offset[9]

0: Cycle Offset8[]

0x2F

CYCLE_TIME_L

7: Cycle Offset[7]

6: Cycle Offset[6]

R/W

CYCLE_TIME.cycle_offset

5: Cycle Offset[5]

4: Cycle Offset[4]

0x00

–

–

3: Cycle Offset[3]

2: Cycle Offset[2]

1: Cycle Offset[1]

0: Cycle Offset[0]