S1R72803F00A

EPSON

77

RxORBAreaStart

This register sets the starting address of a receive ORB data area.

TxHeaderAreaStart

This register sets the starting address of a transmit header area.

TxStreamAreaStart

This register sets the starting address of a transmit stream data area.

TxStreamAreaEnd

This register sets the ending address of a transmit stream data area. The actual data store area is up to

immediately before this specified address.

RxStreamAreaStart

This register sets the starting address of a receive stream data area.

Bus Reset Header Pointer Register

This Bus Reset Header Pointer Register holds the value of a PostRxHdrPtr when a bus reset occurs. When

several bus resets occur, it is updated to the latest PostRxHdrPtr. This register is read-only and writing to this

register is ignored.

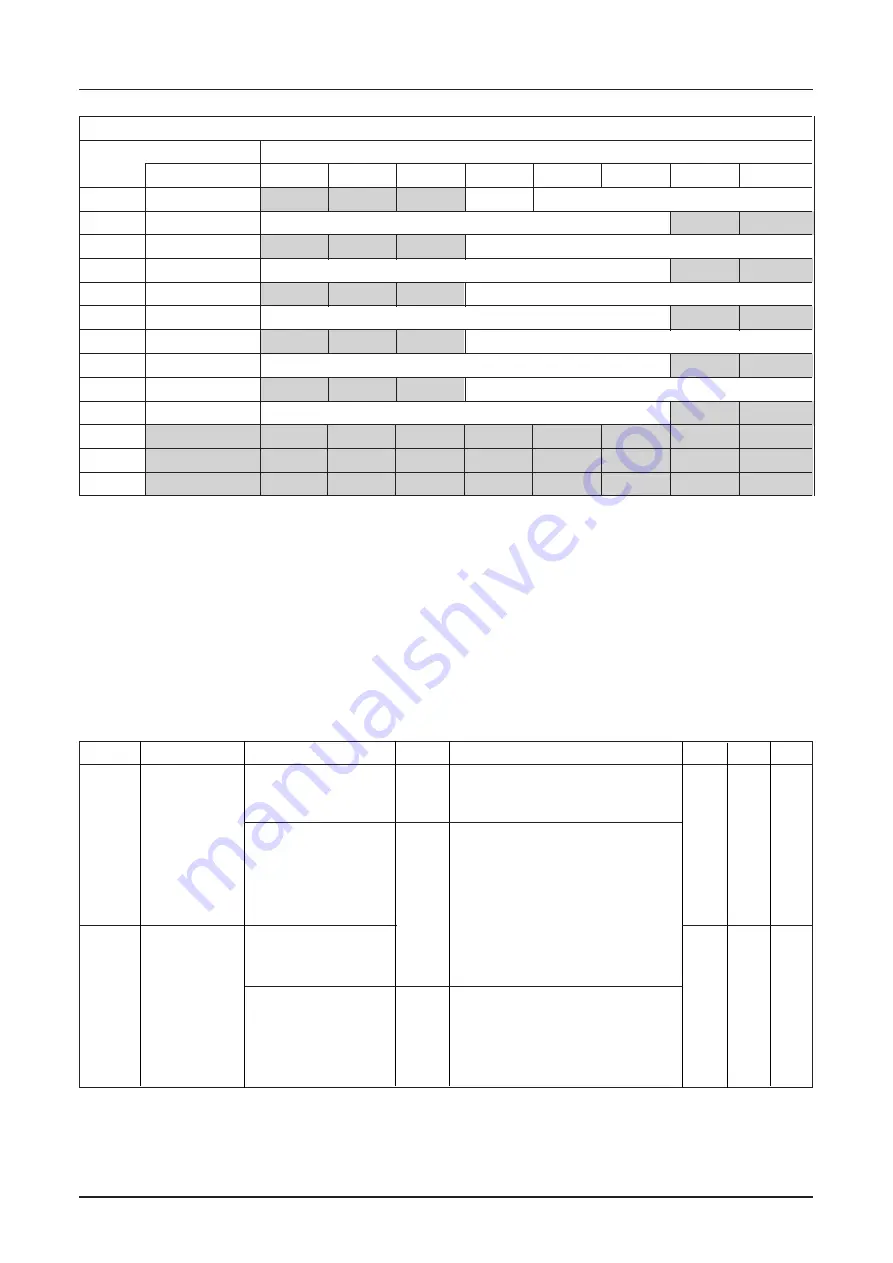

Address Register Name

Bit Symbol

R/W

Description

H.Rst S.Rst B.Rst

0x58

BRstHdrPtr_H

7:

Write is ignore

6:

Read is always zero

5:

4: BusResetPtr[12]

0x00

0x00

–

3: BusResetPtr[11]

2: BusResetPtr[10]

Bus Reset Header Area Pointer

1: BusResetPtr[9]

R

This register indicates Address

0: BusResetPtr[8]

in Rx Header Area

0x59

BRstHdrPtr_L

7: BusResetPtr[7]

when BusRest detected.

6: BusResetPtr[6]

5: BusResetPtr[5]

4:

0x00

0x00

–

3:

Write is ignore

2:

Read is always zero

1:

0:

Memory Map Area Index/Window Register

AreaIndex

AreaWindow_H/L

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

0x00

RxORBAreaStart_H

(MSB)

RxORBAreaStart[12:8]

RxORBAreaStart_L

RxORBAreaStart[7:2]

(LSB)

0x01

TxHdrAreaStart_H

(MSB)

TxHdrAreaStart[12:8]

TxHdrAreaStart_L

TxHdrAreaStart[7:2]

(LSB)

0x02

TxStreamAreaStart_H

(MSB)

TxStreamAreaStart[12:8]

TxStreamAreaStart_L

TxStreamAreaStart[7:2]

(LSB)

0x03

TxStreamAreaEnd_H

(MSB)

TxStreamAreaEnd[12:8]

TxStreamAreaEnd_L

TxStreamAreaEnd[7:2]

(LSB)

0x04

RxStreamAreaStart_H

(MSB)

RxStreamAreaStart[12:8]

RxStreamAreaStart_L

RxStreamAreaStart[7:2]

(LSB)

0x05

(Reserved)

:

(Reserved)

0x0F

(Reserved)