Schematics

S5U13706B00C Rev. 1.0 Evaluation Board

Seiko Epson Corporation

25

Rev. 5.1

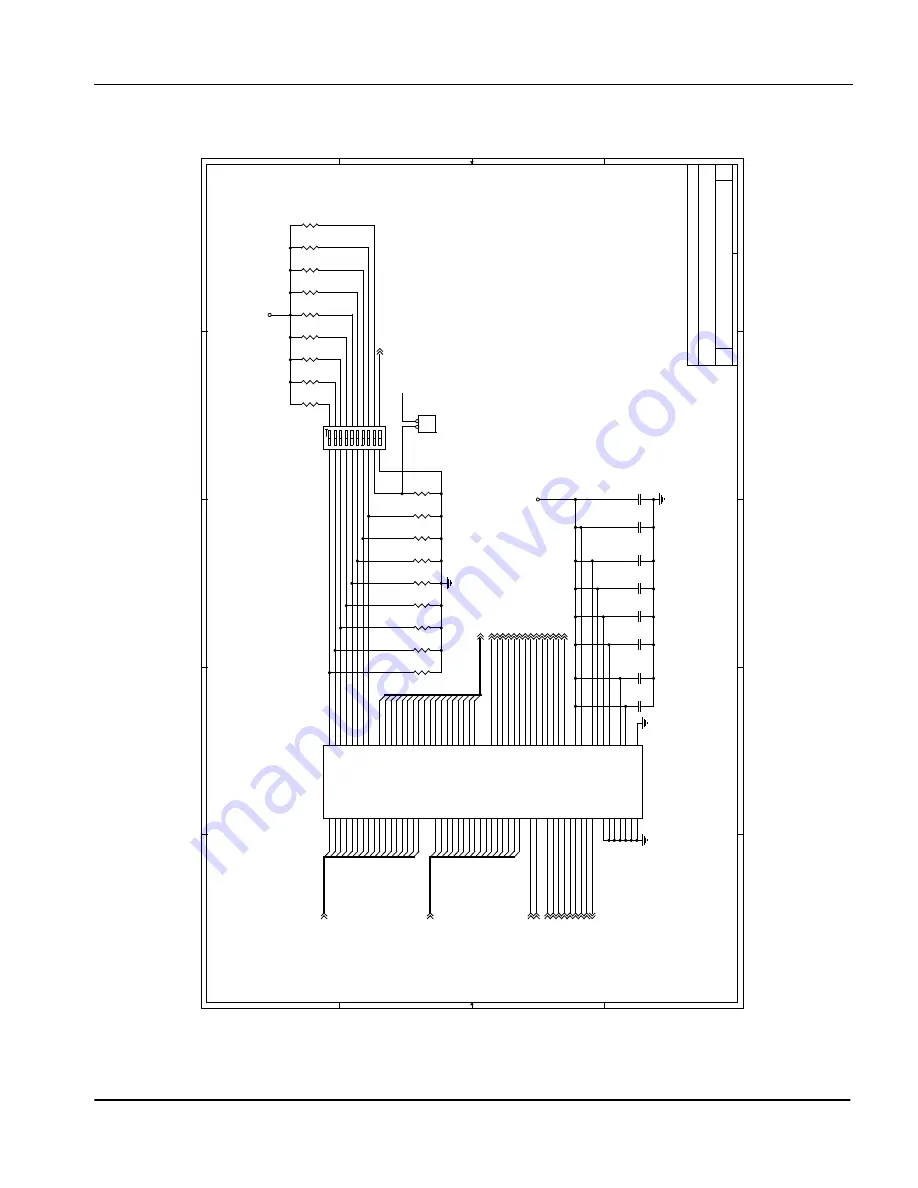

9 Schematics

Figure 9-1: S1D13706B00C Schematics (1 of 6)

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

<D

oc>

1

.1

S

5

U

13706B

00C

R

e

v.

1.

0 -

S

1

D

13706F00A

/D

IP

S

W

B

16

W

edne

sday,

M

a

rc

h

08

, 2000

Ti

tle

S

ize

D

o

cum

ent

N

u

m

ber

R

e

v

Da

te

:

S

heet

of

DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 DB8 DB9 DB1

0

DB1

1

DB1

2

DB1

3

DB1

4

DB1

5

A

B

[16:

0]

D

B

[15:

0]

FP

D

A

T13

FP

D

A

T5

FP

D

A

T8

FP

D

A

T1

FP

D

A

T0

FP

D

A

T16

FP

D

A

T14

FP

D

A

T11

FP

D

A

T17

FP

D

A

T3

FP

D

A

T7

FP

D

A

T9

FP

D

A

T4

FP

D

A

T2

FP

D

A

T10

FP

D

A

T6

FP

D

A

T12

FP

D

A

T15

GP

IO

0

AB0 AB1 AB2 AB3 AB4 AB5 AB6 AB7 AB8 AB9 AB1

0

AB1

1

AB1

2

AB1

3

AB1

4

AB1

5

AB1

6

A

B

[16:

0]

5,

6

D

B

[15:

0]

5,

6

CL

K

I2

2

CL

K

I

2,

5,

6

WA

IT

#

5,

6

RD/

W

R

#

5,

6

RES

E

T

#

5,

6

WE

1

#

5,

6

WE

0

#

5,

6

RD#

5,

6

BS#

5,

6

M/

R

#

5,

6

CS#

5,

6

FP

D

A

T[

17:

0]

3

FP

FR

AM

E

3

FP

LI

N

E

3

FP

SH

IF

T

3

DR

DY

3

CV

OU

T

3,

4

PW

M

O

U

T

3

GP

O

3,

4

GP

IO

0

3

GP

IO

1

3

GP

IO

2

3

GP

IO

3

3

GP

IO

4

3

GP

IO

5

2,

3

GP

IO

6

2,

3

nC

O

N

FI

G

6

+3.

3

V

+3.

3

V

R1

2

330K

R1

0

330K

R4

15K

R1

3

330K

U1

S

1

D

13706F

00A

5 4 3 2 99 98 97 96 95 94 93 92 91 90 89 88 87

35 34 33 32 31 30 29 28 27 24 23 22 21 20 19 18

15 77

6 7 8 9 10 11 12 13 17

85 84 83 82 81 80 79 78

55 56 57 58 59 60 61 64 65 66 67 68 69 70 71 72 73 74

52 53 54 48 46 38 47 45 44 43 42 41 40 39

86

14 25 36 50 62 75 100

16 26

37 49 63 76

1 51

AB0 AB1 AB2 AB3 AB4 AB5 AB6 AB7 AB8 AB9 AB1

0

AB1

1

AB1

2

AB1

3

AB1

4

AB1

5

AB1

6

DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 DB8 DB9 DB1

0

DB1

1

DB1

2

DB1

3

DB1

4

DB1

5

CL

KI

CL

KI

2

CS# M/

R

#

BS# RD# WE

0

#

WE

1

#

RD/

W

R

#

RES

E

T

#

WA

IT

#

CN

F

0

CN

F

1

CN

F

2

CN

F

3

CN

F

4

CN

F

5

CN

F

6

CN

F

7

FP

D

A

T0

FP

D

A

T1

FP

D

A

T2

FP

D

A

T3

FP

D

A

T4

FP

D

A

T5

FP

D

A

T6

FP

D

A

T7

FP

D

A

T8

FP

D

A

T9

FPD

A

T10

FPD

A

T11

FPD

A

T12

FPD

A

T13

FPD

A

T14

FPD

A

T15

FPD

A

T16

FPD

A

T17

FPF

R

AM

E

FP

L

IN

E

FP

SH

IF

T

D

RDY

CVO

U

T

PW

M

O

U

T

GP

0

GP

IO

0

GP

IO

1

GP

IO

2

GP

IO

3

GP

IO

4

GP

IO

5

GP

IO

6

T

ESTE

N

VSS VSS VSS VSS VSS VSS VSS

HI

OVD

D

HI

OVD

D

NI

OVD

D

NI

OVD

D

NI

OVD

D

NI

OVD

D

CO

RE

VDD

CO

RE

VDD

R1

4

330K

C1 0.

1u

R1

5

330K

C2 0.

1u

R1

6

330K

C3 0.

1u

R9

15K

R1

7

330K

C4 0.

1

u

R6

15

K

R1

8

330K

C5 0.

1u

C6 0.

1u

C7 0.

1u

R7

15K

C8 0.

1u

SW

1

SW

D

IP-

1

0

1 2 3 4 5 6 7 8 9

20 19 18 17 16 15 14 13 12 11

10

R3

15K

R5

15K

JP

1

HEAD

ER

2

1

2

R2

15K

R8

15K

R1

15

K

R1

1

330K