Page 28

Epson Research and Development

Vancouver Design Center

SED1352

Hardware Functional Specification

X16-SP-001-16

Issue Date: 99/07/28

7 A.C. CHARACTERISTICS

Conditions: V

DD

= 3.0V ± 10%, 3.3V ± 10% or V

DD

= 5.0V ± 10%

T

A

= -40

°

C to 85

°

C

T

rise

and

T

fall

for all inputs must be < 5 nsec (10% ~ 90%)

C

L

= 80pF (Bus/MPU Interface)

C

L

= 100pF (LCD Panel Interface)

C

L

= 20pF (Display Memory Interface)

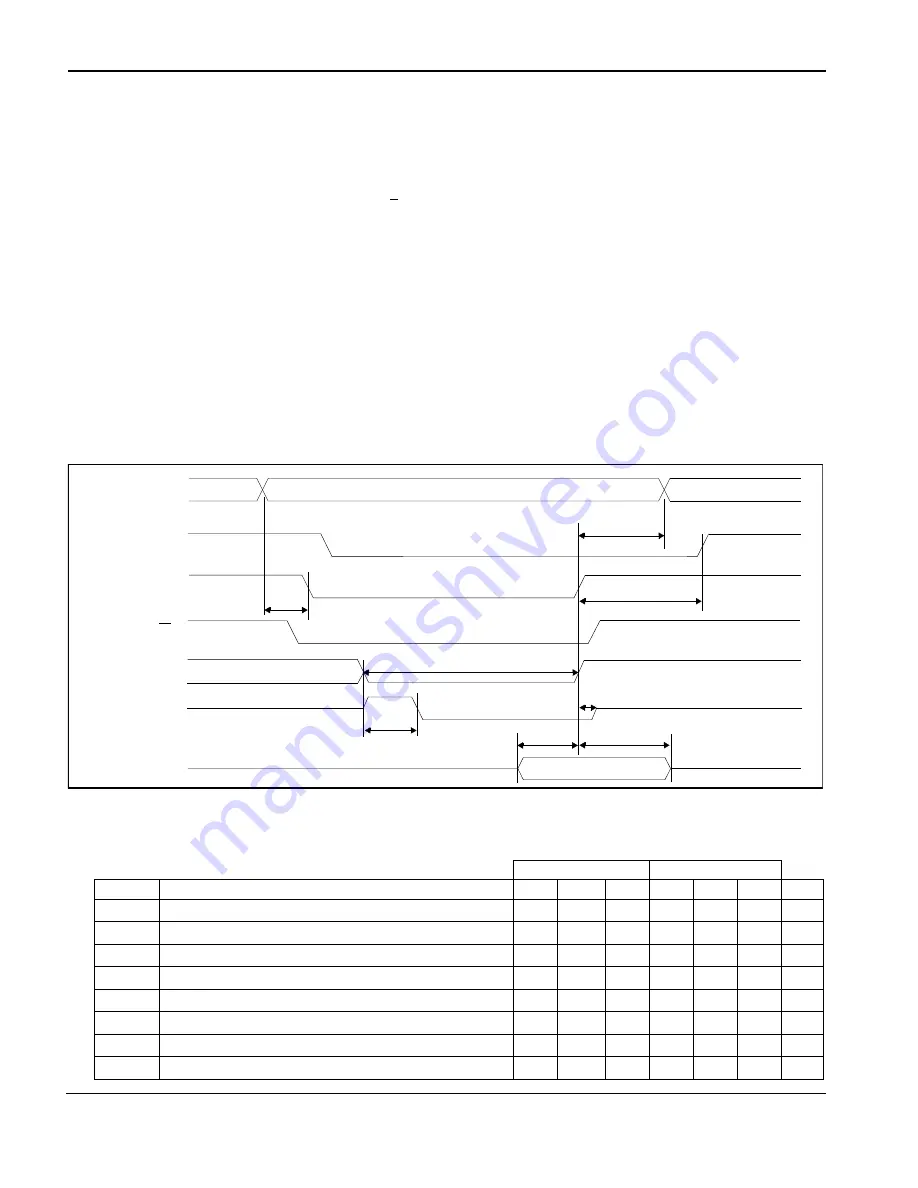

7.1 Bus Interface Timing

7.1.1 MC68000 Interface Timing

Note

All input timing parameters are based on a maximum 16MHz bus clock.

IOW# Timing

Figure 10: IOW# Timing (68000)

Table 7-1: IOW# Timing (68000)

3V/3.3V

5V

Symbol

Parameter

Min

Typ

Max

Min

Typ

Max Units

t1

AB[9:1] valid before AS# falling edge

10

0

ns

t2

AB[9:1] hold from AS# rising edge

20

10

ns

t3

IOCS# hold from AS# rising edge

0

0

ns

t4

UDS#/LDS# valid before AS# rising edge

30

20

ns

t5

UDS#/LDS# falling edge to DTACK# falling edge

40

25

ns

t6

AS# rising edge to DTACK# hi-z delay

45

25

ns

t7

DB[15:0] setup to AS# rising edge

20

10

ns

t8

DB[15:0] hold from AS# rising edge

20

10

ns

AB[9:1]

AS#

UDS#/LDS#

VALID

VALID

t2

t6

t3

t1

DB[15:0]

R/W

DTACK#

t5

t4

IOCS#

t7

t8

Hi-Z

Hi-Z

Hi-Z

Hi-Z

INVALID