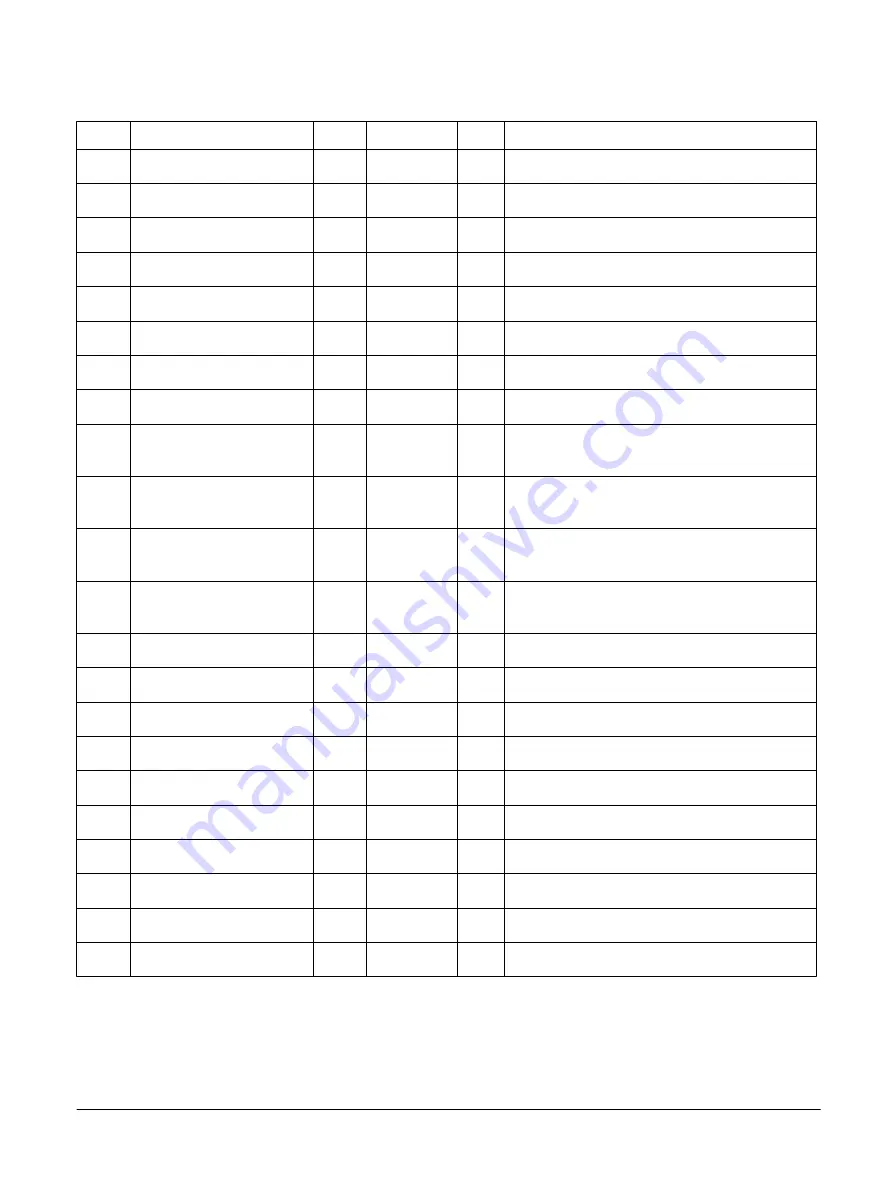

Table 4-32 SCC registers summary (continued)

Offset

Name

Type

Reset

Width Description

0x01D8

SCDBG_CTRL

RW/RO

0x0000_0000

32

See

.

0x01DC

EXP_IF_CTRL

RW

0x0000_0000

32

See

0x01E4

RO_CTRL

RW

0x0000_0001

32

See

0x01E8

CMN_CCIX_CTRL

RW/RO

0x0101_0000

32

See

.

0x01EC

STM_CTRL

RW

0x0000_0000

32

See

.

0x01F0

AXI_OVRD_PCIE

RW

0x0030_3030

32

See

.

0x01F4

AXI_OVRD_CCIX

RW

0x0030_3030

32

See

0x01F8

AXI_OVRD_TSIF

RW

0x0000_3030

32

See

.

0x0200

TRACE_PAD_CTRL0

RW

0x1111_1111

32

See

4.5.80 TRACE_PAD_CTRL0 Register

0x0204

TRACE_PAD_CTRL1

RW

0x0000_1111

32

See

4.5.81 TRACE_PAD_CTRL1 Register

0x0208

IOFPGA_TMIF_PAD_CTRL

RW

0x0011_1111

32

See

4.5.82 IOFPGA_TMIF_PAD_CTRL Register

0x020C

IOFPGA_TSIF_PAD_CTRL

RW

0x0011_1111

32

See

4.5.83 IOFPGA_TSIF_PAD_CTRL Register

0x0E00

APB_CTRL_CLR

RW

0xXXXX_XXXX

32

See

0x0FD0

PID4

RO

0x0000_0004

32

See

0xFE0

PID0

RO

0x0000_00AF

32

See

0xFE4

PID1

RO

0x0000_00B0

32

See

0xFE8

PID2

RO

0x0000_000B

32

See

0xFEC

PID3

RO

0x0000_0000

32

See

0xFF0

CID0

RO

0x0000_000D

32

See

0xFF4

CID1

RO

0x0000_00F0

32

See

0xFF8

CID2

RO

0x0000_0005

32

See

0xFFC

CID3

RO

0x0000_00B1

32

See

4.5.2

PMCLK_DIV Register

The PMCLK_DIV Register characteristics are:

Purpose

Controls the

PMCLK

division value from

REFCLK

.

4 Programmers model

4.5 Serial Configuration Control registers

101489_0000_02_en

Copyright © 2019, 2020 Arm Limited or its affiliates. All rights

reserved.

4-124

Non-Confidential - Beta