Configurations

Available in all N1 board configurations.

Memory offset and full register reset value

See

4.7.1 APB energy meter registers summary

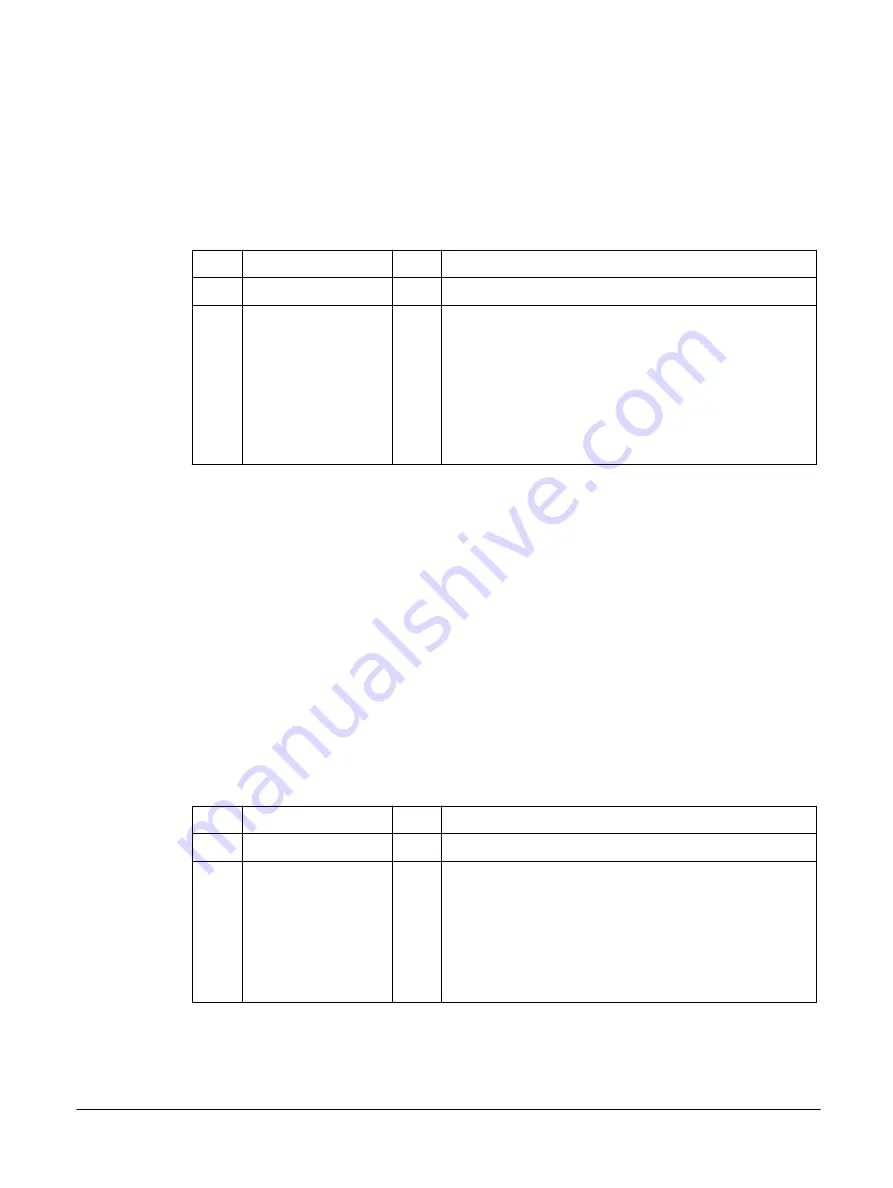

The following table shows the bit assignments.

Table 4-142 SYS_V_SYS Register bit assignments

Bits

Name

Type

Function

[31:12] -

-

Reserved.

[11:0]

SYS_V_SYS

RO

12

‑

bit representation of the instantaneous supply voltage of the

parts of the N1 SoC, outside the clusters, that operate from the

VSYS power supply:

•

Full scale measurement, 4096, represents 2V5. Full scale is

0xFFF

.

•

Measured voltage = (SY1)/1622 volts.

•

The

CB_nRST

reset signal resets the register to zero. The

register then updates every 100µs after the reset.

4.7.7

SYS_V_CL0 Register

The SYS_V_CL0 Register characteristics are:

Purpose

Contains a 12

‑

bit representation of the instantaneous supply voltage of N1 SoC cluster 0.

Usage constraints

This register is read

‑

only.

Configurations

Available in all N1 board configurations.

Memory offset and full register reset value

See

4.7.1 APB energy meter registers summary

The following table shows the bit assignments.

Table 4-143 SYS_V_CL0 Register bit assignments

Bits

Name

Type

Function

[31:12] -

-

Reserved.

[11:0]

SYS_V_CL0

RO

12

‑

bit representation of the instantaneous supply voltage of N1

SoC cluster 0:

•

Full scale measurement, 4096, represents 2V5. Full scale is

0xFFF

.

•

Measured voltage = (SY1)/1622 volts.

•

The

CB_nRST

reset signal resets the register to zero. The

register then updates every 100µs after the reset.

4.7.8

SYS_V_PCIE Register

The SYS_V_PCIE Register characteristics are:

4 Programmers model

4.7 APB energy meter registers

101489_0000_02_en

Copyright © 2019, 2020 Arm Limited or its affiliates. All rights

reserved.

4-211

Non-Confidential - Beta