ETAS

Technical Data

XETK-S22.0 - User’s Guide

47

7.7

Test Characteristics

7.8

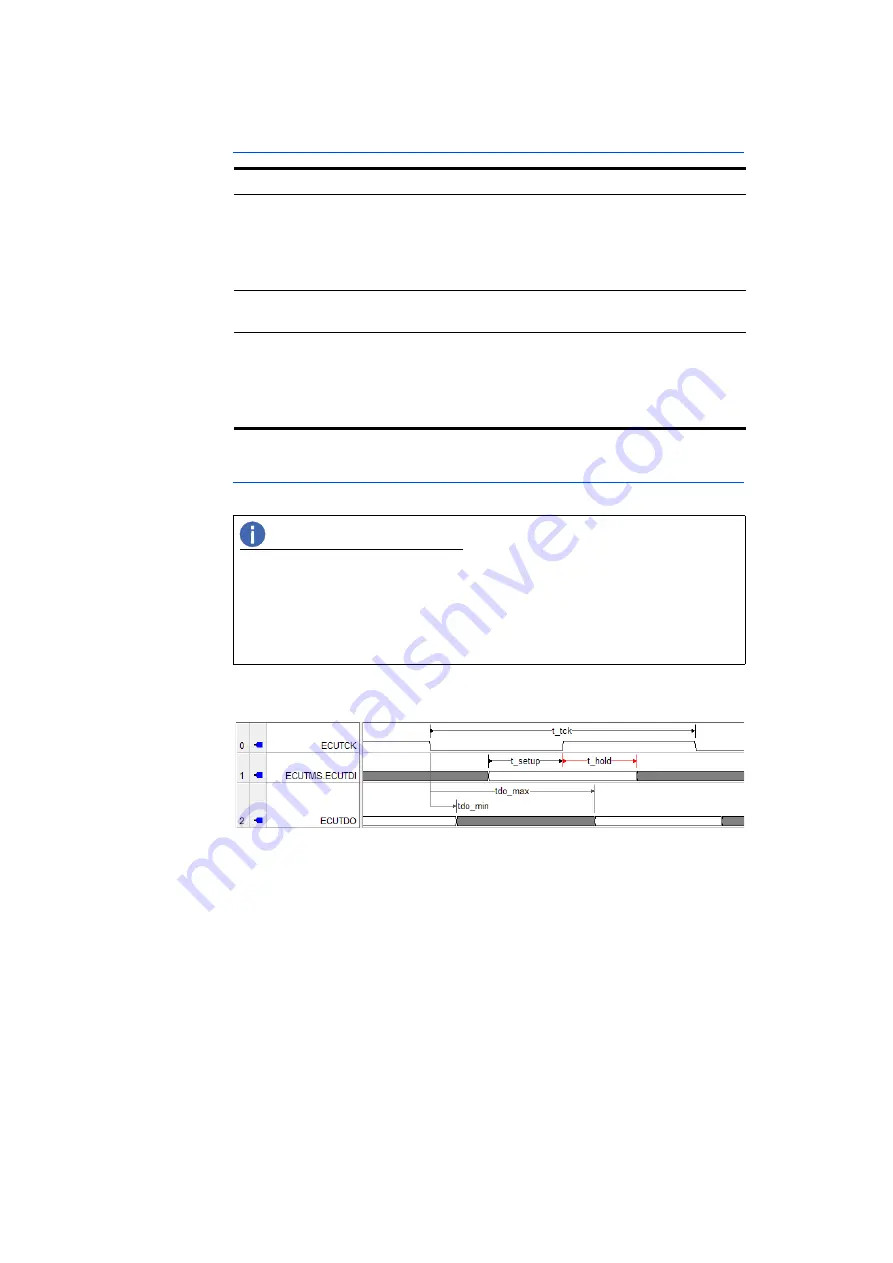

JTAG Timing Characteristics

The following diagrams show the timings the XETK-S22.0 can process.

7.8.1

JTAG Timing Diagram

Parameter

Symbol Condition

Min Typ

Max Unit

Reset delay 1

1)

t

Reset1

U

Batt

= 12 V

VDDP = 0 V

3.3 V/

5.0 V

without transferring

FPGA

26

50

ms

Reset delay 2

2)

t

Reset2

U

Batt

= 0 V

12 V

transfer FPGA

100

300 ms

1)

Delay of ECU reset through the XETK without transferring the FPGA (U

Batt

present, VDDP will be switched on)

2)

max. delay of ECU reset through the XETK (U

Batt

and VDDP will be switched

on)

NOTE

JTAG timing parameters in this chapter refer to the JTAG interface (CON1) of

the XETK-S22.0. The JTAG wiring to the ECU (ETAN1) must be taken into

account additionally.

All timings are measured at a reference level of 1.5 V. Output signals are mea-

sured with 20 pF to ground and 50

to 1.5 V.