SD20-G Series

232

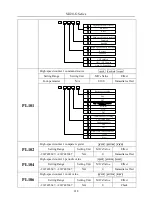

Po001

get the 32-bit result, storing to no.3 and no.4

registers in R area respectively, of which no.6 and

no.5 store to high 32-bit, no.4 and no.3 store to low

32-bit;

MULDPP P1 P2 R3

R6 R5 R4 R3=Po002

Po001*Po003 Po002

Multiplying the value of 2 registers in P area, get

32-bit result, storing to no.3 and no.4 registers in R

area respectively, of which no.6 and no.5 store to

high 32-bit, no.4 and no.3 store to low 32-bit;

(4)

Division Instruction

There are 12 division instructions, which have 16-bit division and 32-bit division, see details as below:

a)

16-bit Division

Instruction format: [DIVW□□ X Y Z]

Instruction Description:

DIVW is division instruction,□□is instruction execution register area, X is

divisor, Y is dividend, Z is store result area; The result of instruction execution is Z=X/Y, which means

that the value of register address in X area divided by the value of register address in Y area, the result

sends to Z register address, of which integer of divisor stores to low-bit register address, remainder stores

to high-bit register address; User can operate for R area, P area and immediate operand; See details as

table 8.1.9.

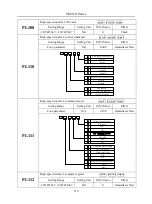

Table 8.1.9 16-bit Division Instruction Syntax, Results and related Annotations

Syntax Expression

Running Results

Annotations

DIVWRR R1 R2 R3

R3=R1/R2

R4=R1%R2

Dividing the value of 2 registers in R area, integer stores to

no.3 register, remainder stores to no.4 register.

DIVWDR D1 R2 R3

R3=1/R2

R4=1%R2

Dividing immediate operand and the value of R register,

integer stores to no.3 register, remainder stores to no.4

register.

DIVWPR P1 R2 R3

R3=Po001/R2

R4=Po001%R2

Dividing the value of P register and R register, integer stores

to no.3 register, remainder stores to no.4 register.

DIVWDP D1 P2 R3

R3=1/Po002

R4=1%Po002

Dividing immediate operand and the value of P register,

integer stores to no.3 register, remainder stores to no.4

register.

DIVWRP R1 P2 R3

R3=R1/Po002

R4=R1%Po002

Dividing the value of R register and P register, integer stores

to no.3 register, remainder stores to no.4 register.

DIVWPP P1 P2 R3

R3=Po001/Po002

R4=Po001%Po00

Dividing the value of 2 registers in P area, integer stores to

no.3 register, and remainder stores to no.4 register.

Summary of Contents for SD20-G Series

Page 35: ...SD20 G Series 35 M3 structure Fig 3 1 5 Servo drive structure 3...

Page 36: ...SD20 G Series 36 ML3 structure 118 5 5 7 5 93 297 8 223 118 93 0 5 12 5 7 5 4 M4...

Page 38: ...SD20 G Series 38 M4 structure Approx mass 10 365 kg Fig 3 1 7 Servo drive structure 5...

Page 39: ...SD20 G Series 39 M5 structure Approx msaa 11 1Kg Fig 3 1 8 Servo drive structure 6...

Page 40: ...SD20 G Series 40 M6 structure Approx mass 17 4Kg Fig 3 1 9 Servo drive structure 7...

Page 182: ...SD20 G Series 182 Fig 6 4 44SD20E Cam internal frameworkdiagram...