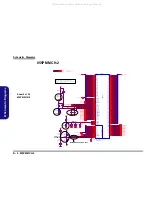

Schematic Diagrams

DDR Termination B - 9

B.Sch

e

m

a

tic D

iag

rams

DDR Termination

Sheet 8 of 36

DDR Termination

+1.25VS

+1.25VS

+1.25VS

+1.25VS

M_DATA_R_[63:0] 8

M_CB_R[7:0] 8

+1.25VS

5,26,27,30,35

M_DATA[63:0]

5

M_CB[7:0]

5

M_DQS_R[8:0] 8

M_DQS[8:0]

5

M_CS0#

5,8

M_CAS#

5,8

M_AA9

5,8

M_CS1#

5,8

M_AA12

5,8

M_CKE3

5,8

M_RAS#

5,8

M_CS3#

5,8

M_CKE1

5,8

M_CS2#

5,8

M_WE#

5,8

M_AA10

5,8

M_AA1

5,8

M_BS0#

5,8

M_AA3

5,8

M_AA7

5,8

M_AA5

5,8

M_AA11

5,8

M_AA8

5,8

M_BS1#

5,8

M_AA0

5,8

M_AA2

5,8

M_AA4

5,8

M_AA6

5,8

M_CKE0

5,8

M_CKE2

5,8

M_AA11

5,8

M_AA_FR_11 8

M_CAS#

5,8

M_RAS#

5,8

M_RAS_FR# 8

M_AA_FR_0 8

M_CAS_FR# 8

M_AA0

5,8

M_BS1#

5,8

M_BS1_FR# 8

M_AA_FR_12 8

M_AA12

5,8

M_AA_FR_9 8

M_AA5

5,8

M_AA9

5,8

M_AA_FR_3 8

M_AA_FR_5 8

M_AA3

5,8

M_AA7

5,8

M_AA_FR_7 8

M_BS0#

5,8

M_WE#

5,8

M_AA_FR_10 8

M_WE_FR# 8

M_AA_FR_1 8

M_AA10

5,8

M_AA1

5,8

M_BS0_FR# 8

M_AA8

5,8

M_AA6

5,8

M_AA_FR_8 8

M_AA4

5,8

M_AA_FR_6 8

M_AA_FR_4 8

M_AA_FR_2

8

M_AA2

5,8

M_DATA_R_43

M_DATA_R_33

M_CB_R5

M_DATA_R_32

M_DATA_R_42

M_DQS_R4

M_DATA_R_52

M_DATA_R_38

M_DATA_R_39

M_DATA_R_53

M_CB_R4

M_DATA_R_40

M_DATA_R_[63:0]

M_CB_R[7:0]

M_DATA_R_34

M_AA_FR_8

M_AA8

+1.25VS

M_AA11

M_AA_FR_11

M_AA6

M_AA_FR_6

M_AA4

M_AA_FR_4

M_DATA[63:0]

M_CB[7:0]

M_DQS_R[8:0]

M_DQS[8:0]

M_DATA_R_54

M_DQS_R6

M_CB_R7

M_DATA_R_11

M_DATA_R_48

M_DATA_R_51

M_DQS_R5

M_DATA_R_46

M_DATA_R_41

M_DATA_R_44

M_DATA_R_47

M_DATA_R_50

M_DATA_R_49

M_DATA_R_45

M_DATA_R_17

M_DQS_R3

M_DATA_R_28

M_DATA_R_35

M_DATA_R_31

M_DATA_R_16

M_DATA_R_23

M_DATA_R_29

M_DATA_R_30

M_DATA_R_21

M_DQS_R2

M_DATA_R_15

M_DATA_R_20

M_DQS_R1

M_DATA_R_22

M_DATA_R_25

M_DATA_R_19

M_AA3

M_AA5

M_DATA_R_24

M_DATA_R_18

M_DATA_R_40

M_DQS_R8

M_DATA_R_49

M_DATA_R_38

M_CB_R4

M_DATA_R_60

M_DQS_R4

M_DATA_R_46

M_CB_R2

M_DATA_R_55

M_DATA_R_47

M_DATA_R_53

M_DATA_R_58

M_DATA_R_57

M_DATA_R_54

M_DATA_R_48

M_CB_R1

M_DATA_R_59

M_DATA_R_41

M_DATA_R_50

M_DQS_R6

M_DATA_R_51

M_DATA_R_52

M_DATA43

M_DATA49

M_CB1

M_CB4

M_DATA54

M_DQS8

M_CB2

M_DATA58

M_DATA52

M_DATA60

M_DATA41

M_DATA47

M_DATA56

M_DATA55

M_DATA46

M_CB0

M_DATA48

M_DQS6

M_DATA53

M_DATA50

M_DATA57

M_DATA59

M_DQS4

M_DATA40

M_DATA38

M_DATA51

M_DATA36

M_DATA37

M_DATA42

M_DATA_R_43

M_DATA_R_34

M_DATA_R_4

M_DATA_R_45

M_DATA_R_10

M_AA2

M_DATA_R_25

M_DATA_R_1

M_DATA_R_19

M_DQS_R0

M_DATA_R_30

M_DATA_R_8

M_DATA_R_20

M_DATA_R_35

M_DATA_R_13

M_DATA_R_33

M_DATA_R_11

M_DATA_R_26

M_DATA_R_6

M_DATA_R_27

M_DATA_R_0

M_DATA_R_42

M_DATA_R_32

M_DATA_R_5

M_DATA_R_9

M_AA_FR_0

M_DATA_R_24

M_DQS_R5

M_DATA26

M_DATA33

M_DATA25

M_DATA13

M_DATA35

M_DATA27

M_DQS3

M_AA_FR_2

M_DATA0

M_DATA5

M_DQS0

M_DATA30

M_AA0

M_DATA19

M_DATA20

M_DATA8

M_DATA6

M_DATA1

M_DATA32

M_DATA24

M_DATA11

M_DATA9

M_DATA10

M_DATA34

M_DATA4

M_DQS5

M_DATA39

M_DATA_R_3

M_DATA_R_2

M_DATA2

M_DATA3

M_AA_FR_12

M_AA_FR_7

M_AA_FR_5

M_AA_FR_3

M_AA_FR_1

M_AA_FR_9

M_AA10

M_AA7

M_AA5

M_AA3

M_AA12

M_AA1

M_AA9

M_DQS2

M_DATA_R_21

M_DATA17

M_DATA18

M_DATA_R_18

M_DATA_R_17

M_DQS_R2

M_DATA21

M_DQS1

M_DATA14

M_DATA_R_15

M_DATA_R_14

M_DATA12

M_DATA_R_12

M_DQS_R1

M_DATA15

M_DQS_R3

M_AA_FR_10

M_DATA_R_36

M_DATA_R_37

M_DATA_R_39

M_DATA44

M_DATA_R_44

M_DATA45

M_DATA_R_4

M_DATA_R_6

M_DQS_R0

M_DATA_R_5

M_DATA_R_14

M_DATA_R_13

M_DATA_R_12

M_DATA_R_7

M_CB_R0

M_DATA_R_36

M_DATA_R_27

M_DATA_R_26

M_DQS_R8

M_CB_R3

M_AA1

M_AA9

M_DATA_R_37

M_CB_R2

M_AA7

M_CB_R1

M_AA12

M_AA8

M_DATA_R_0

M_AA2

M_DQS_R7

M_DATA_R_62

M_AA6

M_AA11

M_DATA_R_3

M_DATA_R_2

M_DATA_R_63

M_AA0

M_DATA_R_1

M_AA4

M_DATA_R_59

M_DATA_R_56

M_DATA_R_58

M_DATA_R_57

M_CB_R6

M_DATA16

M_DATA_R_16

M_DATA7

M_DATA_R_7

M_CB3

M_CB_R3

M_DATA_R_61

M_DATA_R_55

M_DATA_R_60

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_AA10

M_DATA_R_56

M_CB7

M_CB_R6

M_CB6

M_CB_R7

M_DATA_R_62

M_DATA63

M_DATA_R_61

M_DATA62

M_DATA_R_63

M_DQS_R7

M_DQS7

M_DATA61

M_CB_R5

M_CB5

M_CB_R0

M_DATA_R_31

M_DATA31

M_DATA_R_28

M_DATA_R_22

M_DATA23

M_DATA22

M_DATA_R_23

M_DATA29

M_DATA_R_29

M_DATA28

Z0901

Z0902

Z0903

Z0904

Z0905

Z0906

Z0907

Z0908

Z0909

RP40

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP35

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP32

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP17

8P4RX22

8

1

7

2

6

5

3

4

R10

*10(2512)

RP36

8P4RX56

8

1

7

2

6

5

3

4

RP38

8P4RX22

8

1

7

2

6

5

3

4

T

T

T

RP34

8P4RX22

8

1

7

2

6

5

3

4

RP39

8P4RX22

8

1

7

2

6

5

3

4

T

T

T

T

T

T

RP15

8P4RX22

8

1

7

2

6

5

3

4

RP29

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP9

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP7

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP4

8P4RX56

8

1

7

2

6

5

3

4

RP18

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP11

8P4RX22

8

1

7

2

6

5

3

4

RP12

8P4RX22

8

1

7

2

6

5

3

4

RP25

8P4RX56

8

1

7

2

6

5

3

4

C116

.1u(0402)

RP21

8P4RX22

8

1

7

2

6

5

3

4

C24

.1u(0402)

RP14

8P4RX22

8

1

7

2

6

5

3

4

C14

.1u(0402)

C80

.1u(0402)

C82

.1u(0402)

C85

.1u(0402)

C97

.1u(0402)

C23

.1u(0402)

C21

.1u(0402)

RP31

8P4RX22

8

1

7

2

6

5

3

4

C17

.1u(0402)

C89

.1u(0402)

C13

.1u(0402)

C33

.1u(0402)

RP19

10P8RX56

10

9

8

7

6

1

2

3

4

5

C108

.1u(0402)

C38

.1u(0402)

C76

.1u(0402)

C53

.1u(0402)

C27

.1u(0402)

C36

.1u(0402)

C50

.1u(0402)

C111

.1u(0402)

C107

.1u(0402)

C78

.1u(0402)

C83

.1u(0402)

C103

.1u(0402)

RP13

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP3

8P4RX22

8

1

7

2

6

5

3

4

RP20

8P4RX22

8

1

7

2

6

5

3

4

RP30

8P4RX22

8

1

7

2

6

5

3

4

RP2

8P4RX22

8

1

7

2

6

5

3

4

C26

.1u(0402)

RP23

8P4RX22

8

1

7

2

6

5

3

4

RP27

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP37

8P4RX22

8

1

7

2

6

5

3

4

RP24

8P4RX22

8

1

7

2

6

5

3

4

C18

.1u(0402)

RP16

10P8RX56

10

9

8

7

6

1

2

3

4

5

C109

.1u(0402)

C90

.1u(0402)

C41

.1u(0402)

C113

.1u(0402)

C94

.1u(0402)

C95

.1u(0402)

C100

.1u(0402)

RP33

8P4RX22

8

1

7

2

6

5

3

4

C92

.1u(0402)

C60

.1u(0402)

RP22

10P8RX56

10

9

8

7

6

1

2

3

4

5

C16

.1u(0402)

C35

.1u(0402)

C93

.1u(0402)

C112

.1u(0402)

C115

.1u(0402)

C54

.1u(0402)

C74

.1u(0402)

C34

.1u(0402)

C98

.1u(0402)

C43

.1u(0402)

C25

.1u(0402)

C15

.1u(0402)

C91

.1u(0402)

C65

.1u(0402)

RP10

8P4RX22

8

1

7

2

6

5

3

4

RP26

8P4RX22

8

1

7

2

6

5

3

4

RP6

8P4RX22

8

1

7

2

6

5

3

4

R23

22(0402)

R22

22(0402)

C45

.1u(0402)

C64

.1u(0402)

RP1

10P8RX56

10

9

8

7

6

1

2

3

4

5

RP5

8P4RX22

8

1

7

2

6

5

3

4

RP8

8P4RX22

8

1

7

2

6

5

3

4

RP28

8P4RX22

8

1

7

2

6

5

3

4

R15

22(0402)

Place these damping resistors close to SO-DIMM

NOTE: Place these decoupling

capacitors close to VTT_MEM

termination resistors. (one

decoupling capacitor for each

two R-packs)

Place these

decoupling

capacitors on

VTT_MEM trace

VTT_MEM RESISTORS

place test point for all M_CKE & M_CS

signal near VIA on top side as close to

RPACK as possible.

9/12

All manuals and user guides at all-guides.com

all-guides.com

Summary of Contents for M375E MILANO

Page 1: ...All manuals and user guides at all guides com a l l g u i d e s c o m ...

Page 2: ...All manuals and user guides at all guides com ...

Page 40: ...Disassembly 2 16 2 Disassembly All manuals and user guides at all guides com ...

Page 52: ...Part Lists A 12 A Part Lists All manuals and user guides at all guides com ...

Page 90: ...Schematic Diagrams B 38 B Schematic Diagrams All manuals and user guides at all guides com ...