EK-MFR/1 Arch.2573

Rev. E of 22/06/2007

Sh. 33 of 35

501-000658/MN

Eurotek s.r.l.

The label RESET indicates that the RESET signal is active low.

The maximum speed of the internal signal (High_speed_data 0 to 7 and high_speed_clk)

is 53.9 Mb/sec.

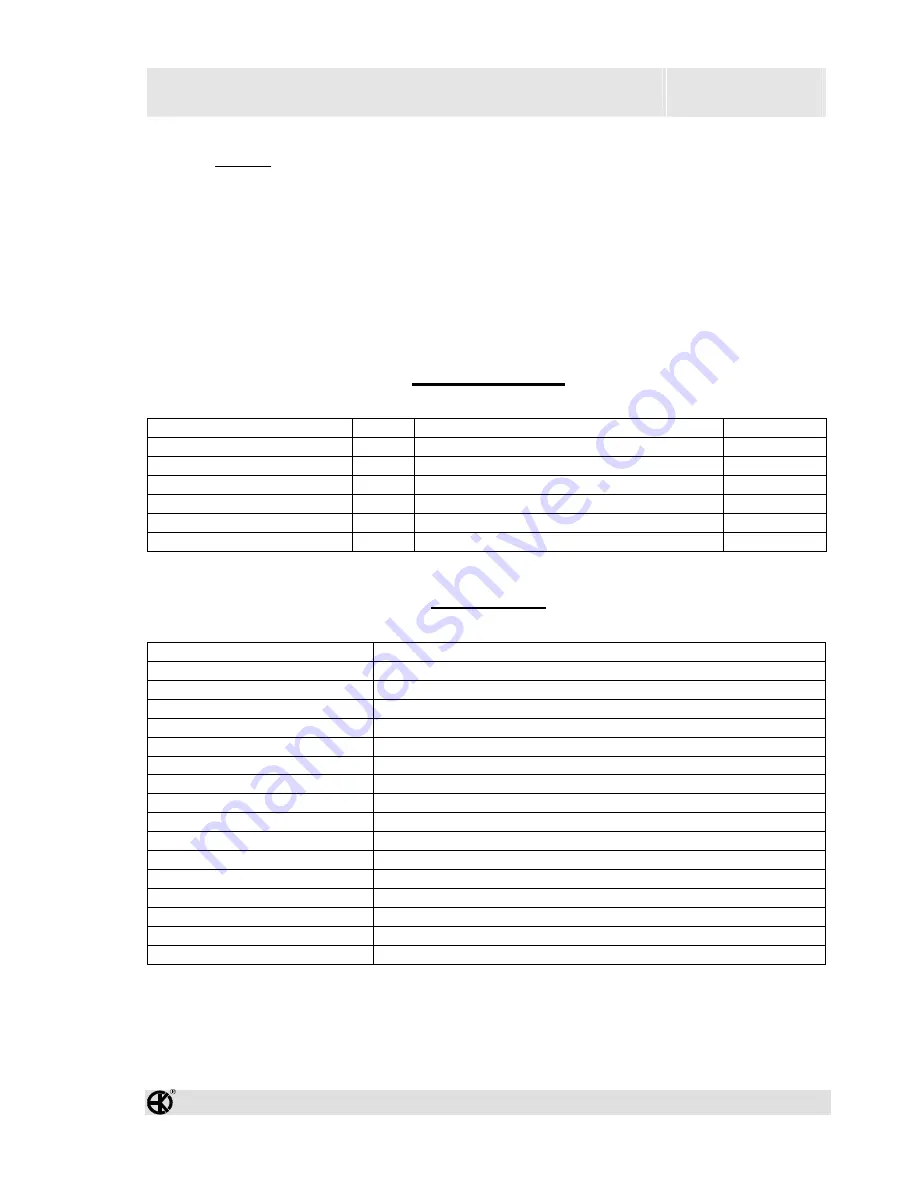

APPENDIX B

EK-MFR/1 peripheral addresses

Addresses Bus :

Range

CS

0x00000000-0x003FFFFF

CS0

Flash (Boot)

4 MByte

0x30000000-0x3FFFFFFF

CS1

FPGA (-CSFPGA_0)

0x30000000-0x3000001F

“

Matrix

0x30000360-0x3000037F

“

Keyboard

0x20000000-0x203FFFFF

CS7

SDRAM

16 Mbyte

0x10000000-0x1FFFFFFF

MBAR

Module Base Address Register

QSPI BUS :

CS

0

1

2

3

4

Slot 0

5

PWS 0 (Relay & SCI enable on PWS/6)

6

PWS 1 (AD & DA converter on PWS/6)

7

Serial EEprom

8

On Screen Display

9

Real Time Clock

A

Slot 5

B

Slot 4

C

Slot 3

D

Slot 2

E

Slot 1

F