Model 5601MSC

Model 5601MSC Master SPG/Master Clock System

OPERATION

Revision 2.2

Page - 37

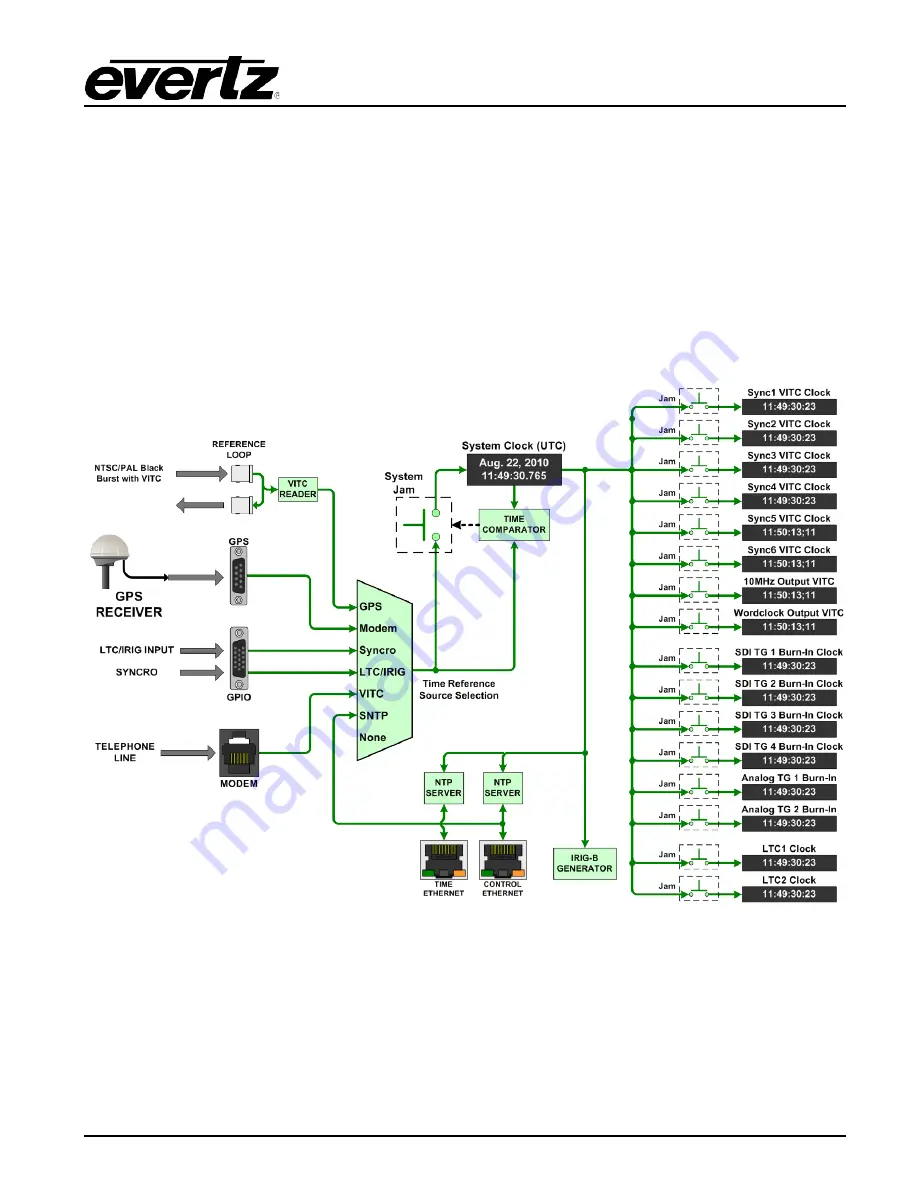

The

system clock

is synchronized to the selected time reference by performing a

time jam

. This is

different than the continuous PLL process that is used for frequency references. The

system clock

in

the 5601MSC runs independently at the frequency provided by the

master oscillator

. Ideally, once the

system clock

has been set, it should keep perfect time forever. In practice stability errors, however

slight, creep in and accumulate over time. Even when locked to GPS or an atomic frequency standard,

leap seconds will occur in UTC time requiring the

system clock

to be occasionally adjusted.

The 5601MSC has several timecode outputs, each of which possess their own clock that runs

independently from the

system clock

. Each of the two LTC outputs and each sync output (including

10MHz and Wordclock) and test generator output have their own independent clock. The timecode

clocks are synchronized to the

system clock

once a day at user specified times. This allows for

timecode rates that do not count in real-time. Note that NTP and IRIG time is derived directly from the

system clock

.

Figure 2-14: Time Locking Block Diagram

The

system clock

time/date is constantly compared to the time/date that is provided by the selected

time reference. Whenever a significant difference is detected, a

system time jam

will be required to

bring the

system clock

back into sync with the time reference. A

system time jam

effectively jams the

time and date acquired from the time reference into the system clock. This effect ripples to all timecode

output clocks jamming them as well. Exactly when a

system time jam

is allowed to take place is

determined by the

Lock Type

that is selected (see section 4.3.10). The amount of difference between

the

system clock

and the time reference must exceed a certain threshold before a system time

jam

is

declared necessary. This threshold is different for each time reference type.