xr

PRELIMINARY

XRT86VL38

REV. P1.0.6

OCTAL T1/E1/J1 FRAMER/LIU COMBO

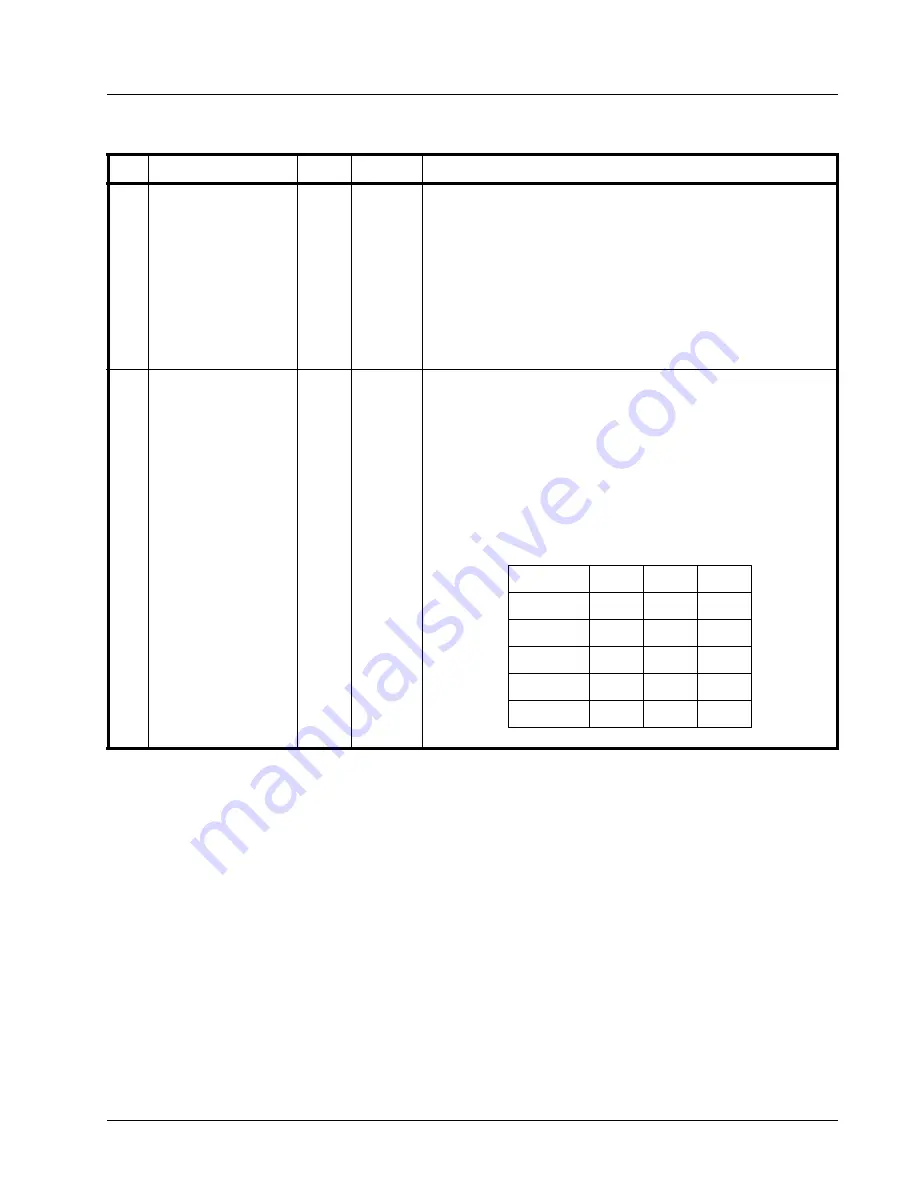

90

3

FASTSYNC

R/W

0

Faster Sync Algorithm

This READ/WRITE bit-field is used to specify one of the synchroniza-

tion criteria. Setting this bit will enable or disable the framing search

engine to declare synchronization earlier.

0 - Setting this bit to ‘0’ will enable the framing search engine to

declare synchronization when 24 consecutive Fe framing bits are

detected without errors.

1 - Setting this bit to ‘1’ will enable the framing search engine to

declare synchronization when 12 consecutive Fe framing bits are

detected without errors.

2

1

0

FS[2]

FS[1]

FS[0]

R/W

R/W

R/W

0

0

0

Framing Select bit 2

Framing Select bit 1

Framing Select bit 0

These three READ/WRITE bit-fields are used to select the DS1 fram-

ing mode. Bit 2 is MSB and Bit 0 is LSB. The following table shows

the five different framing formats that can be selected by configuring

these three bits accordingly.

N

OTE

: Changing framing format will cause a RESYNC to be gener-

ated automatically.

T

ABLE

16: F

RAMING

S

ELECT

R

EGISTER

-T1 M

ODE

R

EGISTER

7- T1 M

ODE

F

RAMING

S

ELECT

R

EGISTER

(FSR) H

EX

A

DDRESS

: 0

X

n107

B

IT

F

UNCTION

T

YPE

D

EFAULT

D

ESCRIPTION

-O

PERATION

Framing

FS[2]

FS[1]

FS[0]

ESF

0

X

X

SF

1

0

1

N

1

1

0

T1DM

1

1

1

SLC

®

96

1

0

0