XRT86VL38

PRELIMINARY

xr

OCTAL T1/E1/J1 FRAMER/LIU COMBO

REV. P1.0.6

145

4

RxFr1544

R/W

0

Receive Fractional/Signaling Interface Enabled

This READ/WRITE bit-field is used to enable or disable the receive fractional

output interface, receive signaling output, the serial channel number output,

as well as the 8kHz and the received recovered clock output. This READ/

WRITE bit-field only functions when the device is configured in base rate.

If the device is configured in base rate:

0 = Setting this bit to ‘0’ will configure the 5 time slot identifier pins

(RxChn[4:0]) to output the channel number in parallel as usual.

1 = Setting this bit to ‘1’ will configure the 5 time slot identifier pins

(RxChn[4:0]) into the following different functions:

RxChn[0] becomes the Receive Serial SIgnaling output pin (RxSIG_n) for sig-

naling outputs. Signaling data can now be output to the RxSIG pin if config-

ured appropriately.

RxChn[1] becomes the Receive Fractional Data Output pin (RxFrTD_n) for

fractional data output. Fractional data can now be output to the RxFrTD pin if

configured appropriately.

RxChn[2] outputs the serial channel number

RxChn[3] outputs an 8kHz clock signal.

RxCHN[4] outputs the received recovered clock signal (1.544MHz for T1,

2.048MHz for E1)

N

OTE

: This READ/WRITE bit-field has no function in the high speed or multi-

plexed modes of operation

3

RxICLKINV

N/A

0

Receive Clock Inversion

This READ/WRITE bit-field selects whether data transition will happen on the

rising or falling edge of the receive clock.

0 = Setting this bit to ‘0’ selects data transition happen on the rising edge of

the receive clocks.

1 = Setting this bit to ‘1’ selects data transition happen on the falling edge of

the receive clocks.

N

OTE

: This feature is only available for base rate configuration (i.e. non-high-

speed, or non-multiplexed modes).

2

RxMUXEN

R/W

0

Receive Multiplexed Mode Enable

This READ/WRITE bit-field enables or disables the multiplexed mode on the

receive side. When multiplexed mode is enable, four channels data from the

line side are multiplexed onto one serial stream and output to the back-plane

interface on RxSER. The backplane speed will become 12.352MHz or

16.384MHz once multiplexed mode is enabled.

0 = Setting this bit to ‘0’ will disable the multiplexed mode.

1 = Setting this bit to ‘1’ will enable the multiplexed mode. Four-channel data

are multiplexed into a single serial stream.

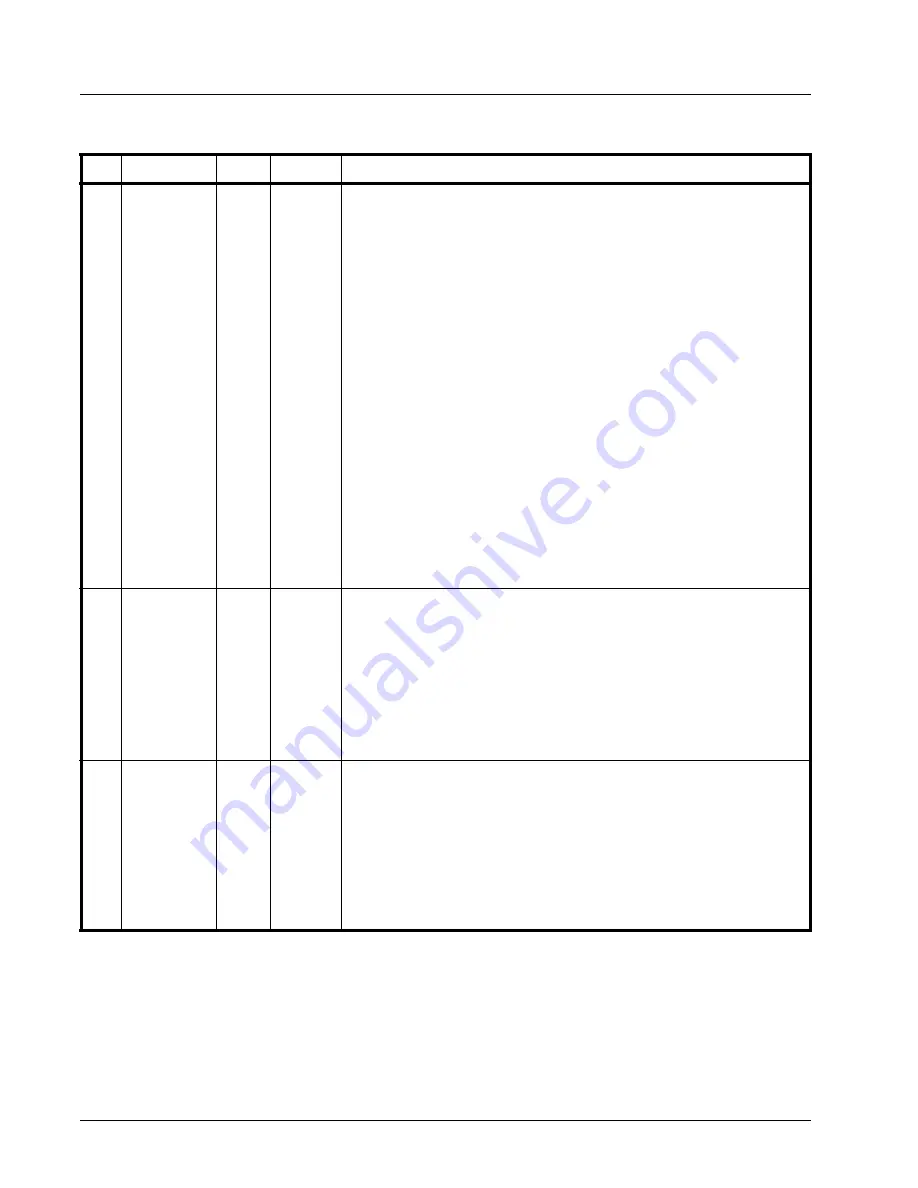

T

ABLE

57: R

ECEIVE

I

NTERFACE

C

ONTROL

R

EGISTER

(RICR) - T1 M

ODE

R

EGISTER

32 - T1 M

ODE

R

ECEIVE

I

NTERFACE

C

ONTROL

R

EGISTER

(RICR) 0

XN

122

B

IT

F

UNCTION

T

YPE

D

EFAULT

D

ESCRIPTION

-O

PERATION