xr

PRELIMINARY

XRT86VL38

REV. P1.0.6

OCTAL T1/E1/J1 FRAMER/LIU COMBO

172

1

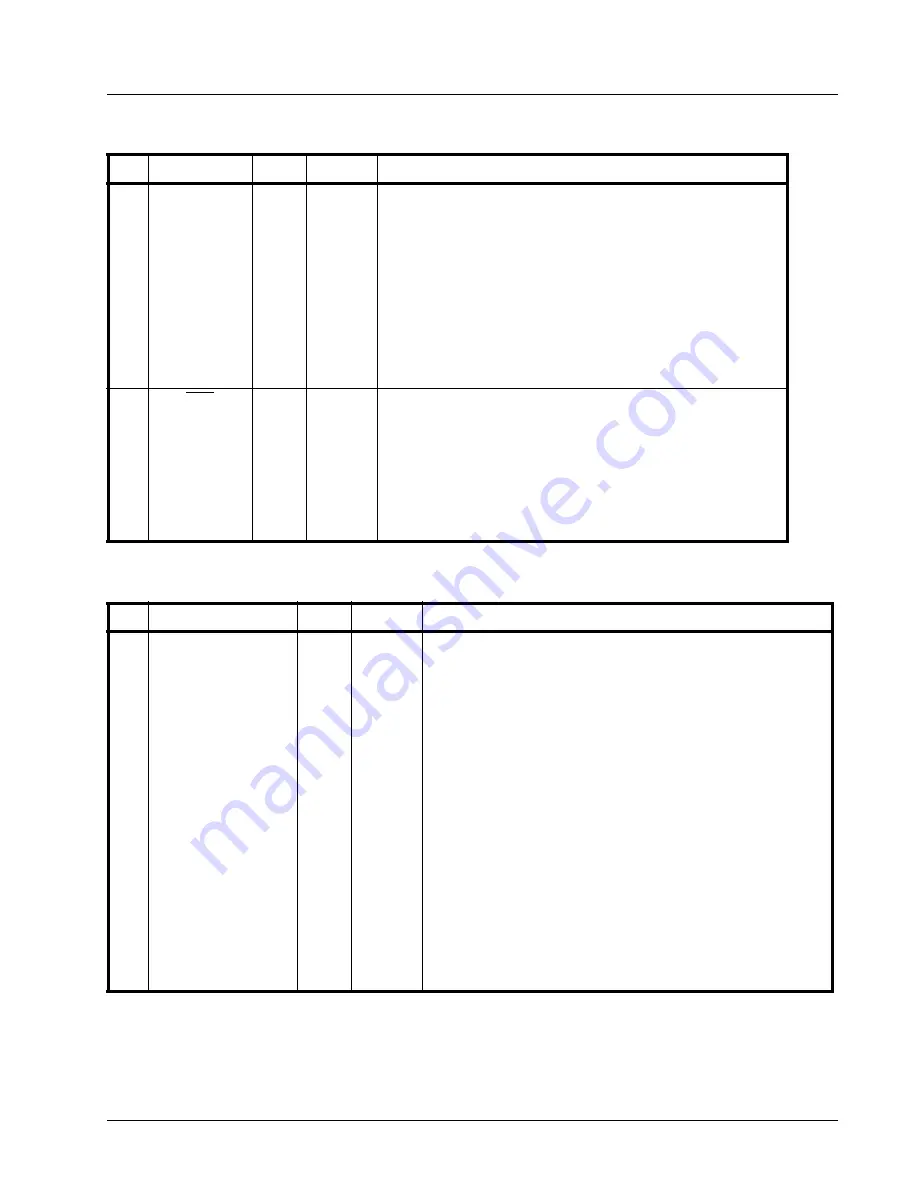

Tx_FCS_EN

R/W

0

Transmit LAPD Message with Frame Check Sequence (FCS)

This READ/WRITE bit-field configures Transmit HDLC 3 Controller

to include or not include the FCS octets in the outbound LAPD mes-

sage frames.

0 = Setting this bit to ‘0’ will configure the Transmit HDLC 3 to not

include the FCS octets into the outbound LAPD message frame.

1 = Setting this bit to ‘1’ will configure the Transmit HDLC 3 to insert

the FCS octets into the outbound LAPD message frame.

N

OTE

: This bit-field is ignored if the transmit HDLC 3 controller has

been configured to operate in the BOS mode - bit-field 0 (MOS/

BOS) within this register is set to 0.

0

MOS/BOS

R/W

0

Message Oriented Signaling/Bit Oriented Signaling Select

This READ/WRITE bit field specifies whether the Transmit /Receive

HDLC 3 Controller will be transmitting/receiving LAPD message

frames (MOS) or Bit Oriented Signal (BOS) messages.

0 = Setting this bit to ‘0’ will configure the Transmit/Receive HDLC 3

Controller to transmit/receive BOS messages.

1 = Setting this bit to ‘1’ will configure the Transmit/Receive HDLC 3

Controller to transmit/receive MOS messages.

T

ABLE

87: T

RANSMIT

D

ATA

L

INK

B

YTE

C

OUNT

R

EGISTER

R

EGISTER

55 T

RANSMIT

D

ATA

L

INK

B

YTE

C

OUNT

R

EGISTER

3 (TDLBCR3) H

EX

A

DDRESS

: 0

X

n154

B

IT

F

UNCTION

T

YPE

D

EFAULT

D

ESCRIPTION

-O

PERATION

7

BUFAVAL//BUFSEL

R/W

0

Transmit HDLC 3 Buffer Available/Buffer Select

This READ/WRITE bit-field has two functions. When this bit is being

written, it specifies which one of the two Transmit HDLC 3 Buffers

has been loaded for transmission. When this bit is read, it indicates

the next available buffer for transmission. The Transmit HDLC 3

Controller should read the next available buffer to generate the next

outbound HDLC 3 message.

0 = Setting this bit to ‘0’ indicates the transmit message data resid-

ing in Transmit HDLC 3 Buffer 0.

0 = Reading a ‘0’ indicates the next available buffer resides in Trans-

mit HDLC 3 Buffer 0.

1 = Setting this bit to ‘1’ indicates the transmit message data resid-

ing in Transmit HDLC 3 buffer 1.

1 = Reading a ‘1’ indicates the next available buffer resides in Trans-

mit HDLC 3 buffer 1.

N

OTE

:

x

If one of these Transmit HDLC 3 buffers contain a message

which has yet to be completely read-in and processed for transmis-

sion by the Tx HDLC 3 controller, then this bit-field will automatically

reflect the value corresponding to the available buffer when it is

read. Changing this bit-field to the in-use buffer is not permitted.

T

ABLE

86: D

ATA

L

INK

C

ONTROL

R

EGISTER

R

EGISTER

54 D

ATA

L

INK

C

ONTROL

R

EGISTER

3 (DLCR3) H

EX

A

DDRESS

: 0

X

n153

B

IT

F

UNCTION

T

YPE

D

EFAULT

D

ESCRIPTION

-O

PERATION