xr

PRELIMINARY

XRT86VL38

REV. P1.0.6

OCTAL T1/E1/J1 FRAMER/LIU COMBO

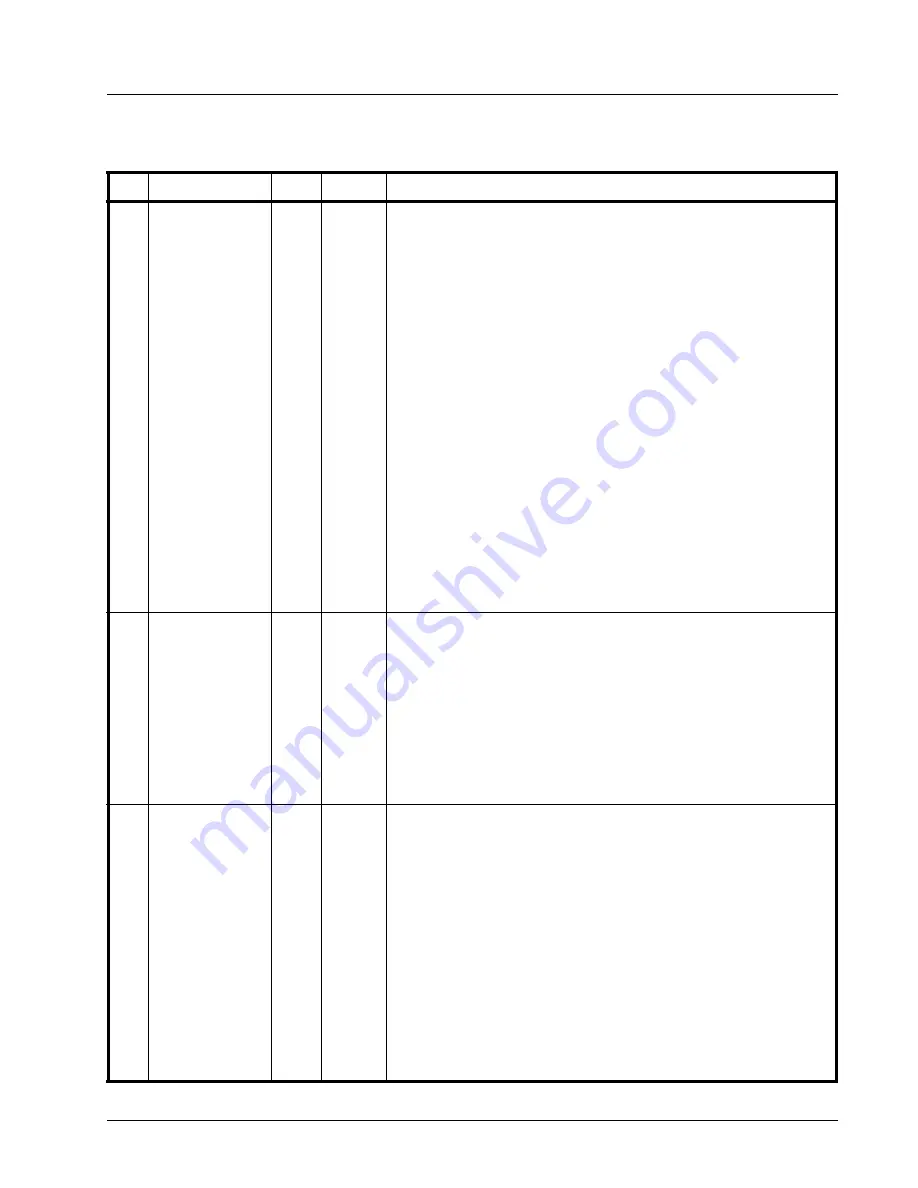

220

1

T

ABLE

129: F

RAMER

I

NTERRUPT

S

TATUS

R

EGISTER

E1 M

ODE

R

EGISTER

531 E1 M

ODE

F

RAMER

I

NTERRUPT

S

TATUS

R

EGISTER

(FISR) H

EX

A

DDRESS

: 0

X

nB04

B

IT

F

UNCTION

T

YPE

D

EFAULT

D

ESCRIPTION

-O

PERATION

7

COMFA Status

RUR/

WC

0

Change of CAS Multiframe Alignment Interrupt Status

This Reset-Upon-Read bit field indicates whether or not the “Change of

CAS multiframe alignment” interrupt has occurred since the last read of

this register.

If this interrupt is enabled, then the Receive E1 Framer block will

generate an interrupt in response to either one of the following

conditions.

1.

Whenever the Receive E1 Framer block declares the “Loss of CAS

Multiframe Alignment”.

2.

Whenever the Receive E1 Framer block clears the “Loss of CAS

Multiframe Alignment”

Loss CAS Multiframe Alignment is declared when the “CASC” number of

consecutive CAS Multiframe Alignment signals have been received in

error, where CASC sets the criteria for Loss of CAS multiframe. CASC can

ben programmed through Framing Control Register (FCR - address

0xn10B, bit 6-5)

0 = Indicates that the “Change of CAS Multiframe Alignment” interrupt has

not occurred since the last read of this register.

1 = Indicates that the “Change of CAS Multiframe Alignment” interrupt has

occurred since the last read of this register.

N

OTES

: This bit only has meaning when Channel Associated Signaling

(CAS) is enabled.

6

NBIT Status

RUR/

WC

0

Change in National Bits Interrupt Status

This Reset-Upon-Read bit field indicates whether or not the “Change in

National Bits” interrupt has occurred since the last read of this register.

If this interrupt is enabled, then the Receive E1 Framer block will

generate an interrupt whenever any one of the National Bits (Sa4-Sa8)

within the incoming non-FAS E1 frames has changed.

0 = Indicates that the “Change in National Bits” interrupt has not occurred

since the last read of this register.

1 = Indicates that the “Change in National Bits” interrupt has occurred

since the last read of this register.

5

SIG Status

RUR/

WC

0

Change in CAS Signaling Bits Interrupt Status

This Reset-Upon-Read bit field indicates whether or not the “Change in

CAS Signaling Bits” interrupt has occurred since the last read of this regis-

ter.

If this interrupt is enabled, then the Receive E1 Framer block will

generate an interrupt whenever any one of the four signaling bits values

(A,B,C,D) has changed in any one of the 30 channels within the incoming

T1 frames. Users can read the signaling change registers (address

0xn10D-0xn110) to determine which signalling channel has changed.

0 = Indicates that the “Change in CAS Signaling Bits” interrupt has not

occurred since the last read of this register.

1 = Indicates that the “Change in CAS Signaling Bits” interrupt has

occurred since the last read of this register.

N

OTE

: This bit only has meaning when Channel Associated Signaling

(CAS) is enabled.