xr

PRELIMINARY

XRT86VL38

REV. P1.0.6

OCTAL T1/E1/J1 FRAMER/LIU COMBO

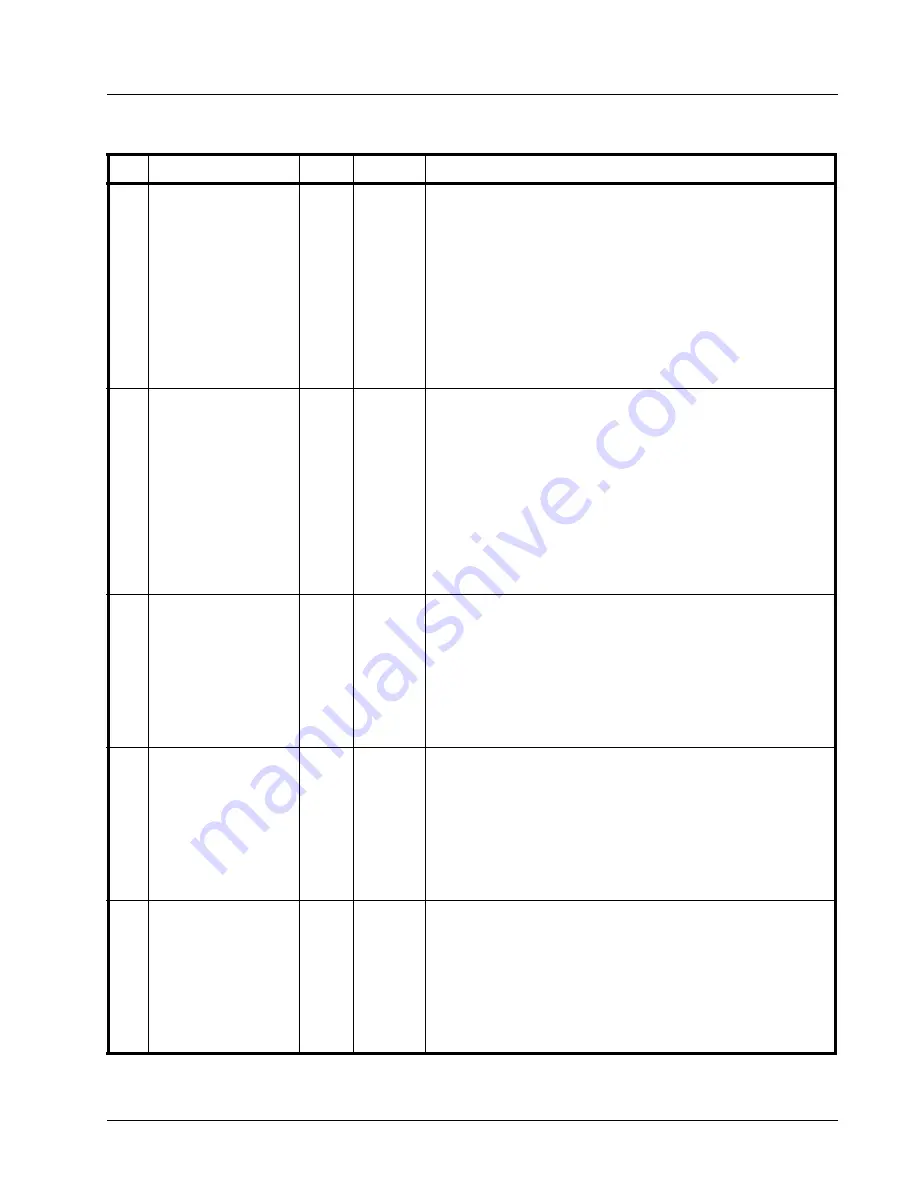

256

4

TxEOT ENB

R/W

0

Transmit HDLC2 Controller End of Transmission (TxEOT) Inter-

rupt Enable

This READ/WRITE bit enables or disables the “Transmit HDLC2

Controller End of Transmission (TxEOT) “Interrupt within the

XRT86VL38 device. Once this interrupt is enabled, the Transmit

HDLC2 Controller will generate an interrupt when it has finished

transmitting a data link message.

0 = Disables the Transmit HDLC2 Controller End of Transmission

(TxEOT) interrupt.

1 = Enables the Transmit HDLC2 Controller End of Transmission

(TxEOT) interrupt.

3

RxEOT ENB

R/W

0

Receive HDLC2 Controller End of Reception (RxEOT) Interrupt

Enable

This READ/WRITE bit enables or disables the “Receive HDLC2

Controller End of Reception (RxEOT) “Interrupt within the

XRT86VL38 device. Once this interrupt is enabled, the Receive

HDLC2 Controller will generate an interrupt when it has finished

receiving a complete data link message.

0 = Disables the Receive HDLC2 Controller End of Reception

(RxEOT) interrupt.

1 = Enables the Receive HDLC2 Controller End of Reception

(RxEOT) interrupt.

2

FCS ERR ENB

R/W

0

FCS Error Interrupt Enable

This READ/WRITE bit enables or disables the “Received FCS Error

“Interrupt within the XRT86VL38 device. Once this interrupt is

enabled, the Receive HDLC2 Controller will generate an interrupt

when it has detected the FCS error within the incoming data link

message.

0 = Disables the “Receive FCS Error” interrupt.

1 = Enables the “Receive FCS Error” interrupt.

1

RxABORT ENB

R/W

0

Receipt of Abort Sequence Interrupt Enable

This READ/WRITE bit enables or disables the “Receipt of Abort

Sequence“ Interrupt within the XRT86VL38 device. Once this inter-

rupt is enabled, the Receive HDLC2 Controller will generate an

interrupt when it has detected the Abort Sequence (i.e. a string of

seven (7) consecutive 1’s) within the incoming data link channel.

0 = Disables the “Receipt of Abort Sequence” interrupt.

1 = Enables the “Receipt of Abort Sequence” interrupt.

0

RxIDLE ENB

R/W

0

Receipt of Idle Sequence Interrupt Enable

This READ/WRITE bit enables or disables the “Receipt of Idle

Sequence“ Interrupt within the XRT86VL38 device. Once this inter-

rupt is enabled, the Receive HDLC2 Controller will generate an

interrupt when it has detected the Idle Sequence Octet (i.e. 0x7E)

within the incoming data link channel.

0 = Disables the “Receipt of Idle Sequence” interrupt.

1 = Enables the “Receipt of Idle Sequence” interrupt.

T

ABLE

146: D

ATA

L

INK

I

NTERRUPT

E

NABLE

R

EGISTER

2

R

EGISTER

546 D

ATA

L

INK

I

NTERRUPT

E

NABLE

R

EGISTER

2 (DLIER2) H

EX

A

DDRESS

: 0

X

nB17

B

IT

F

UNCTION

T

YPE

D

EFAULT

D

ESCRIPTION

-O

PERATION