XRT86VL38

PRELIMINARY

xr

OCTAL T1/E1/J1 FRAMER/LIU COMBO

REV. P1.0.6

289

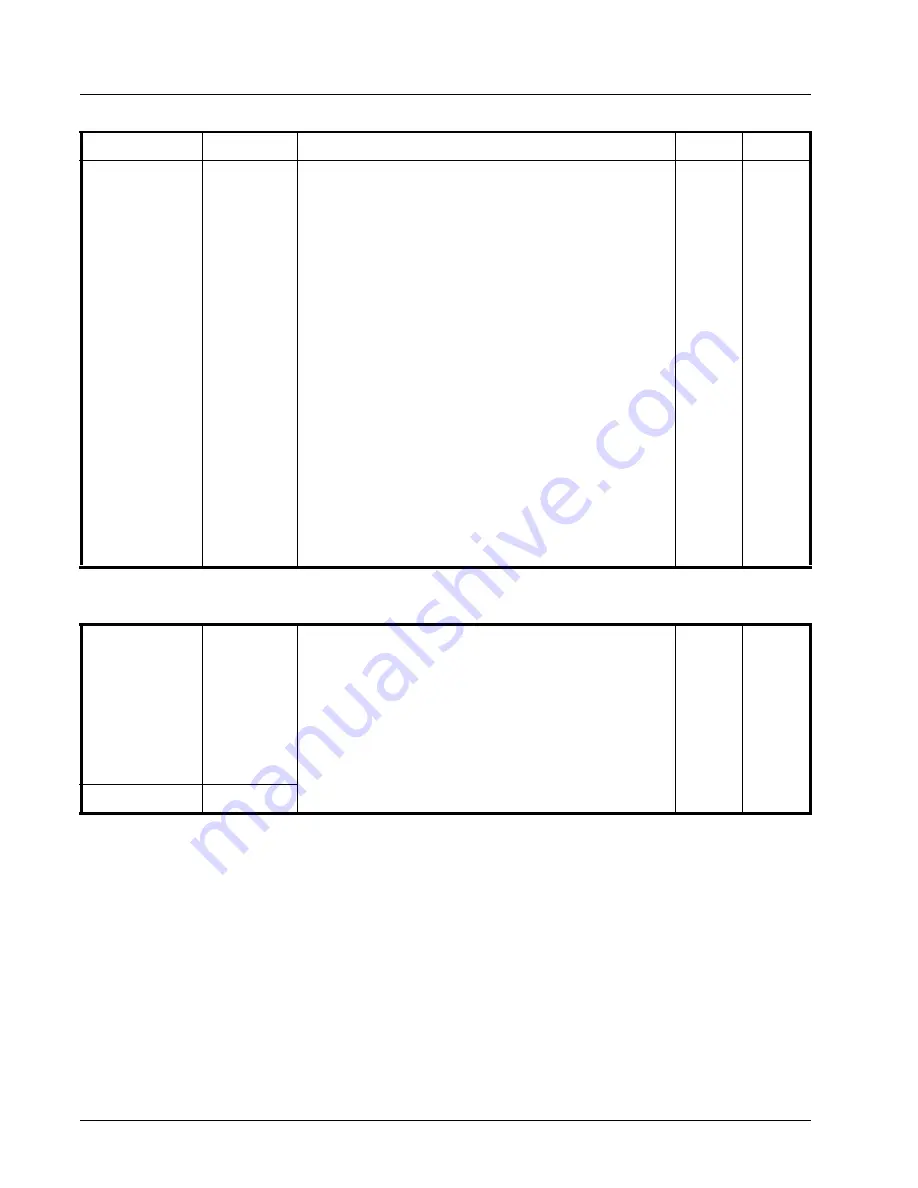

D7

Reserved

R/W

0

D6-D0

B6S6_n -

B0S6_n

Arbitrary Transmit Pulse Shape, Segment 6

These seven READ/WRITE bit-fields form the sixth of the eight

segments of the transmit shape pulse when the XRT86VL38 is

configured in “Arbitrary Mode”.

In T1 mode, arbitrary mode can be selected in T1 short haul

and T1 Gain mode of operations. Arbitrary mode is enabled by

writing the EQC[4:0] bits in register 0x0Fn0 to ‘0x0D’ for T1

short haul arbitrary pulse mode, and writing the EQC[4:0] bits

to ‘0x13’ for T1 Gain mode arbitrary pulse configuration.

In E1 mode, arbitrary mode can be selected in E1 Short Haul,

Long Haul, and Gain Mode of operations. (i.e. EQC[4:0] =

0x18-0x1F) Arbitrary mode is enabled by writing the E1 Arbi-

trary Mode Enable bit (bit D3 within register 0x0FE1) to ‘1’

when the XRT86VL38 device is configured in any E1 EQC set-

tings.

The shape of each channel's transmitted pulse can be made

independently user programmable by selecting the “Arbitrary

Pulse” mode. The arbitrary pulse is divided into eight time seg-

ments whose combined duration is equal to one period of

MCLK.

These seven bits represent the amplitude of the nth channel's

arbitrary pulse in signed magnitude format with Bit 6 as the

sign bit and Bit 0 as the least significant bit (LSB).

R/W

0

T

ABLE

170: M

ICROPROCESSOR

R

EGISTER

#569, 585, 601, 617, 633, 649, 665 & 681 B

IT

D

ESCRIPTION

R

EGISTER

A

DDRESS

0

X

0F0E

H

0

X

0F1E

H

0

X

0F2E

H

0

X

0F3E

H

0

X

0F4E

H

0

X

0F5E

H

0

X

0F6E

H

0

X

0F7E

H

C

HANNEL

_n

C

HANNEL

_0

C

HANNEL

_1

C

HANNEL

_2

C

HANNEL

_3

C

HANNEL

_4

C

HANNEL

_5

C

HANNEL

_6

C

HANNEL

_7

F

UNCTION

R

EGISTER

T

YPE

R

ESET

V

ALUE

Bit #

N

AME

T

ABLE

169: M

ICROPROCESSOR

R

EGISTER

#568, 584, 600, 616, 632, 648, 664 & 680 B

IT

D

ESCRIPTION