xr

PRELIMINARY

XRT86VL38

REV. P1.0.6

OCTAL T1/E1/J1 FRAMER/LIU COMBO

28

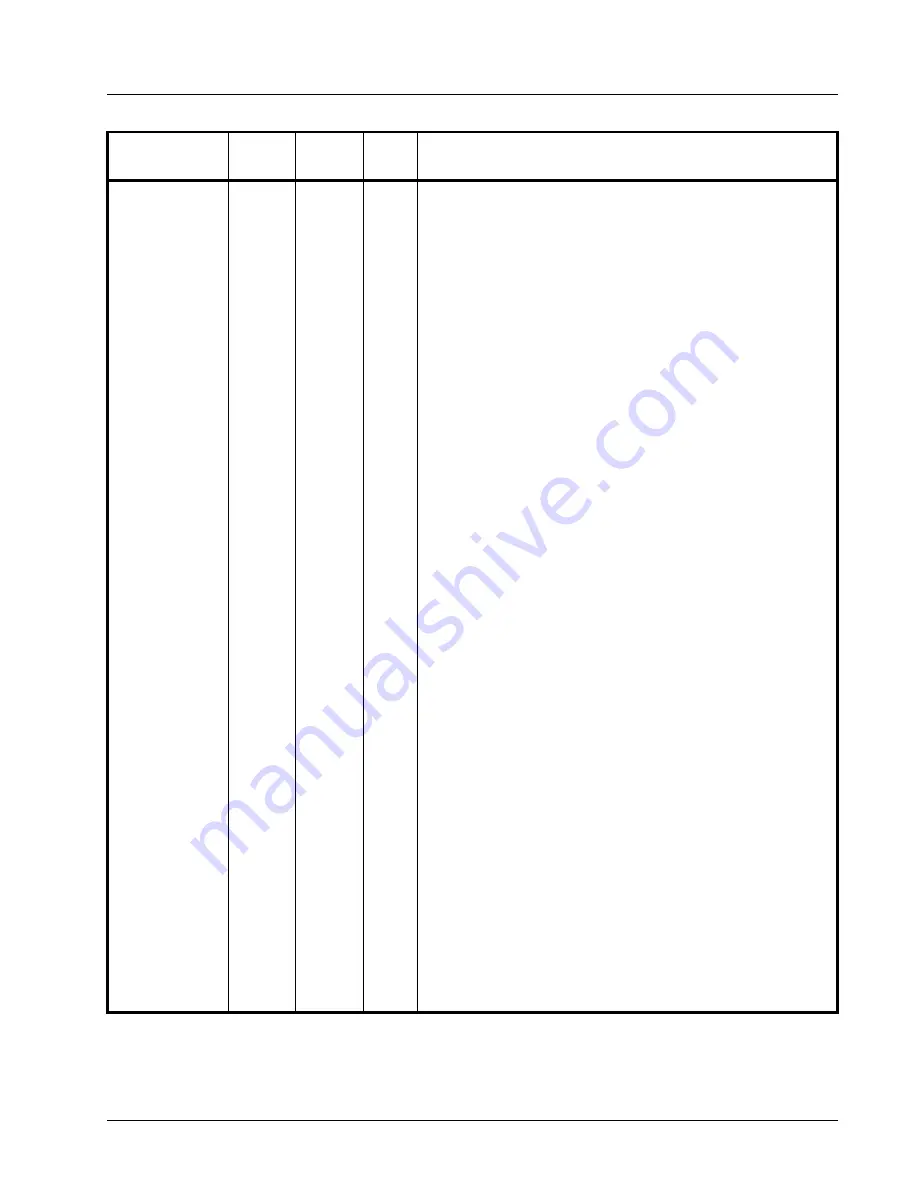

RxSERCLK0/

RxLINECLK0

RxSERCLK1/

RxLINECLK1

RxSERCLK2/

RxLINECLK2

RxSERCLK3/

RxLINECLK3

RxSERCLK4/

RxLINECLK4

RxSERCLK5/

RxLINECLK5

RxSERCLK6/

RxLINECLK6

RxSERCLK7/

RxLINECLK7

A6

B13

C20

H25

AD26

AC19

AB12

AB6

D9

A12

B18

H20

W20

V16

W12

W6

I/O

Receive Serial Clock Signal/Receive Line Clock

This clock signal is used by the Receive payload data output Inter-

face to update the contents on the RxSERn pins. When the

XRT86VL38 is configured in the standard rate mode, data applied to

the RxSER pin can be updated on either the rising edge or the falling

edge of RxSERCLK, which is determined by the RxICLKINV bit (from

register location - 0xn122).

The functions of these RxSERCLKn pins will depend on whether the

XRT86VL38 device is configured in the standard rate or high-speed

modes of operation.

In Standard Rate Mode:

When RxSERCLKn is configured as Input:

These pins will be configured as inputs if the slip buffer is enabled on

the receive path. (i.e. SB_ENB[1:0] = ‘01’ or ‘10’ from register

0xn116)

When the RxSERCLK is configured as input, users must provide a

1.544MHz clock rate to this input pin for T1 mode of operation. If the

XRT86VL38 is configured in E1 mode of operation, users must then

provide a 2.048MHz clock rate to this input pin.

When RxSERCLKn is configured as Output:

These pins will be configured as outpus if the slip buffer is bypassed

on the receive path. (i.e. SB_ENB[1:0] = ‘00’ or ‘11’ from register

0xn116).

When the RxSERCLK is configured as output, it will output a

1.544MHz clock rate when the XRT86VL38 is configured in T1 mode

of operation. The RxSERCLK pin will output a 2.048MHz when the

XRT86VL38 is configured in E1 mode of operation.

DS1/E1 Non-Multiplexed High-Speed Backplane Interface

(RxSERCLK as Input Only)

In the non-multiplexed high-speed interface mode, this pin is used as

the timing source for the high-speed backplane interface to output

high-speed data to the RxSERn pin. Users must configure the

RxSERCLK as input in the non-multiplexed high-spped backplane

mode.

The non-multiplexed high-speed modes supported in DS1 or E1

modes are MVIP 2.048MHz, 4.096MHz, and 8.192MHz.

In MVIP 2.048MHz mode, RxSERCLK will be an input clock signal at

2.048MHz.

In 4.096MHz Non-multiplexed high speed mode, RxSERCLK will be

an input clock signal at 4.096MHz.

In 8.192MHz Non-multiplexed high spped mode, RxSERCLK will be

an input clock signal at 8.192MHz.

N

OTES

:

1.

For DS1 mode, the DS-0 data is mapped into an E1 frame

by ignoring every fourth time slot (don’t care).

2.

These 8 pins are internally pulled “High” for each channel.

RECEIVE SERIAL DATA OUTPUT

S

IGNAL

N

AME

420 P

KG

B

ALL

#

484 P

KG

B

ALL

#

T

YPE

D

ESCRIPTION