xr

PRELIMINARY

XRT86VL38

REV. P1.0.6

OCTAL T1/E1/J1 FRAMER/LIU COMBO

418

13.5

T1 Extended Superframe Format (ESF)

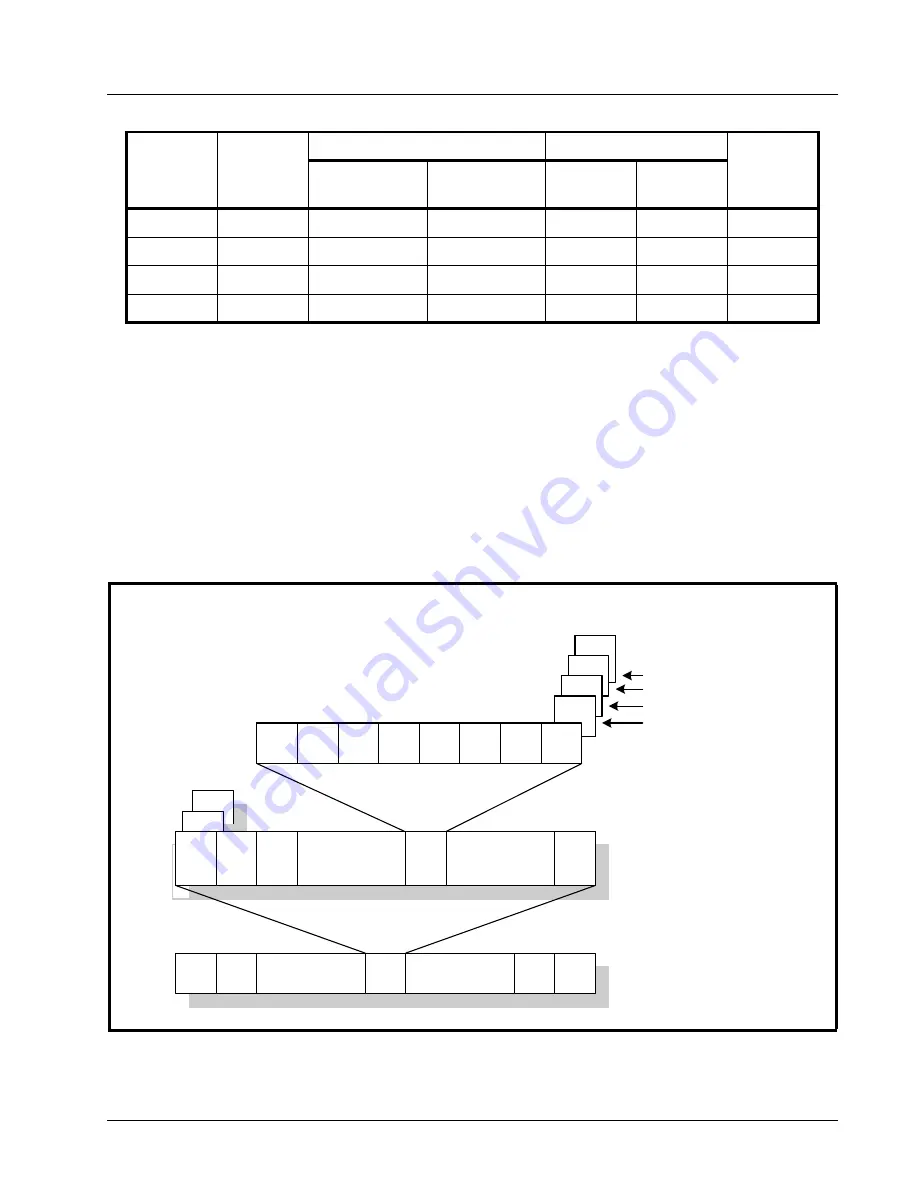

In Extended Superframe Format (ESF), as shown in Figure 115 and Table 190, the multiframe structure is

extended to 24 frames. The timeslot structure is identical to D4 (SF) format. Robbed-bit signaling is

accommodated in frame 6 (A-bit), frame 12 (B-bit), frame 18 (C-bit) and frame 24 (D-bit).

The F-bit pattern of ESF contains three functions:

1.

Framing Pattern Sequence (FPS), which defines the frame and multiframe boundaries.

2.

Facility Data Link (FDL), which allows data such as error-performance to be passed within the T1 link.

3.

Cyclic Redundancy Check (CRC), which allows error performance to be monitored and enhances the reli-

ability of the receiver’s framing algorithm.

9

1544

1

----

1-8

----

----

10

1737

----

1

1-8

----

----

11

1930

0

----

1-8

----

----

12

2123

----

0

1-7

8

B

F

IGURE

115. T1 E

XTENDED

S

UPERFRAME

F

ORMAT

T

ABLE

189: S

UPERFRAME

F

ORMAT

F

RAME

B

IT

F-B

ITS

B

IT

U

SE

IN

E

ACH

T

IMESLOT

S

IGNALLING

C

HANNEL

T

ERMINAL

F

RAMING

F

T

T

ERMINAL

F

RAMING

F

S

T

RAFFIC

S

IG

D

C

CRC

CRC

FD

L

FD

L

B

A

Bit

0

Bit

1

Bit

2

Bit

3

Bit

4

Bit

5

Bit

6

Bit

7

8 Bits per

Timeslot

FP

S

o

rF

s

FPS

or

Fs

TS

1

TS

1

TS

2

TS

2

-----------------

-

-----------------

-

TS

13

TS

13

------------------

-

------------------

-

TS

24

TS

24

FR

1

FR

1

FR

2

FR

2

-----------------

-

-----------------

-

FR

13

FR

13

------------------

-

------------------

-

FR

23

FR

23

FR

24

FR

24

Signalling

Information

Bit 7

During:

Frame 24

Frame 18

Frame 12

Frame 6

24 Timeslots per Frame

Frame = 193 Bits

Multiframe

ESF = 24

Frames