xr

PRELIMINARY

XRT86VL38

REV. P1.0.6

OCTAL T1/E1/J1 FRAMER/LIU COMBO

6

1.0

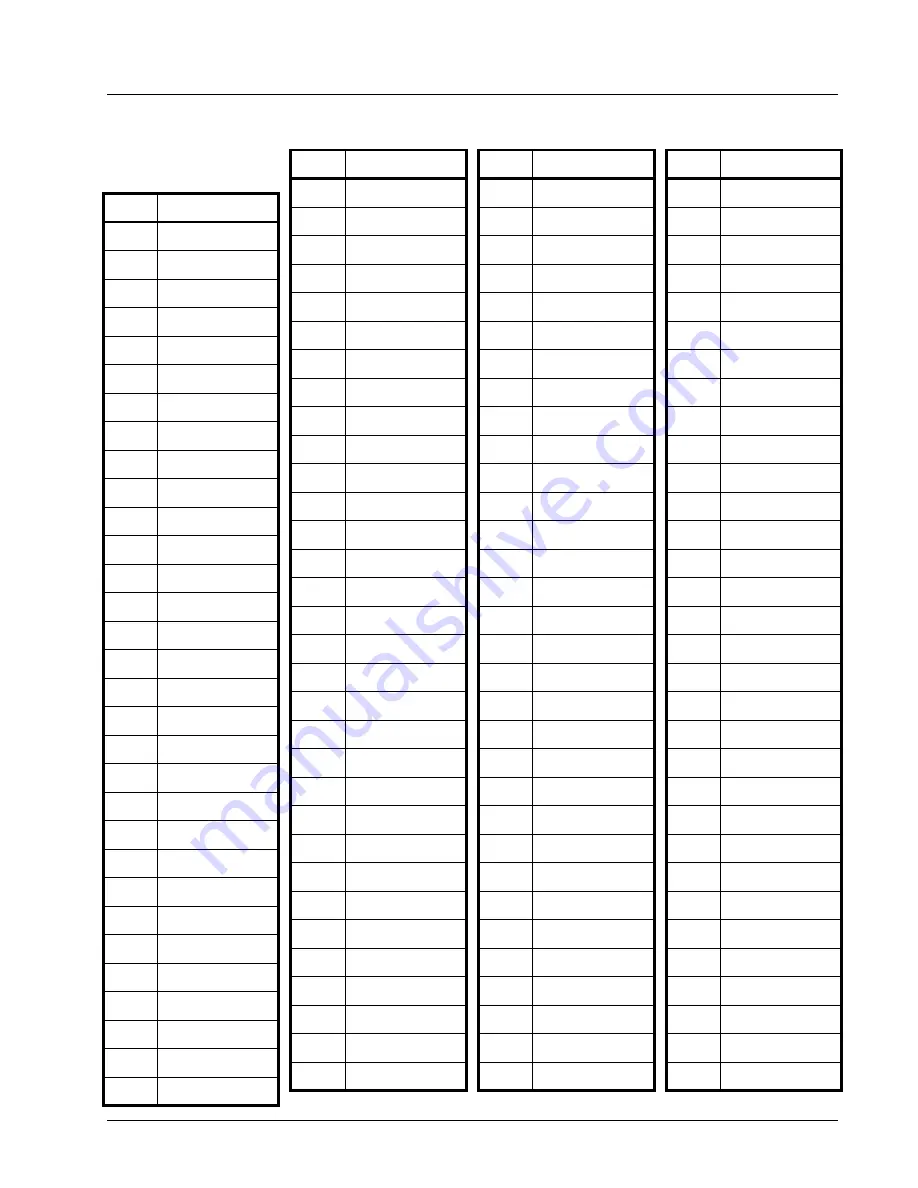

PIN LISTS

T

ABLE

1: 420 B

ALL

L

IST

BY

B

ALL

N

UMBER

P

IN

P

IN

N

AME

A1

DVDD18

A2

DGND

A3

AGND

A4

MCLKIN

A5

TMS

A6

RXSERCLK0

A7

TCK

A8

RXCHCLK0

A9

TXSYNC0

A10

RXCHN0_4

A11

TXSERCLK0

A12

TXCHCLK0

A13

TXCHN0_2

A14

RXCHCLK1

A15

RXCHN1_2

A16

RXLOS1

A17

TXMSYNC1

A18

TXOH1

A19

TXOHCLK1

A20

TXCHN1_3

A21

TXCHN1_4

A22

RXCHN2_0

A23

RXCASYNC2

A24

RXCHCLK2

A25

VDD

A26

RXCHN2_4

B1

VDDPLL18

B2

GNDPLL

B3

NC

B4

AVDD18

B5

E1MCLKOUT

B6

TDO

B7

TRST

B8

RXCRCSYNC0

B9

RXOHCLK0

B10

TXMSYNC0

B11

TEST

B12

TXCHN0_1

B13

RXSERCLK1

B14

RXSER1

B15

RXOH1

B16

RXCHN1_3

B17

VSS

B18

NC

B19

TXCHN1_2

B20

RXLOS2

B21

GPIO1_3

B22

RXCHN2_1

B23

NC

B24

TXSYNC2

B25

VSS

B26

TXCHCLK2

C1

VDDPLL18

C2

VDDPLL18

C3

GNDPLL

C4

NC

C5

ANALOG

C6

VSS

C7

RXSER0

C8

VDD

C9

RXCHN0_2

C10

RXCHN0_3

C11

RXOH0

T

ABLE

1: 420 B

ALL

L

IST

BY

B

ALL

N

UMBER

P

IN

P

IN

N

AME

C12

TXOH0

C13

VSS

C14

TXCHN0_4

C15

VDD

C16

TXSYNC1

C17

RXCHN1_4

C18

TXCHN1_0

C19

TXSERCLK1

C20

RXSERCLK2

C21

RXSER2

C22

RXCHN2_2

C23

RXCHN2_3

C24

TXMSYNC2

C25

VSS

C26

TXCHN2_2

D1

RTIP0

D2

RVDD0

D3

VDDPLL18

D4

JTAG_RING

D5

RxTSEL

D6

T1MCLKOUT

D7

TDI

D8

RXCHN0_0

D9

RXSYNC0

D10

VSS

D11

TXSER0

D12

TXCHN0_0

D13

RXCRCSYNC1

D14

RXCHN1_0

D15

RXSYNC1

D16

RXOHCLK1

D17

TXSER1

T

ABLE

1: 420 B

ALL

L

IST

BY

B

ALL

N

UMBER

P

IN

P

IN

N

AME

D18

TXCHN1_1

D19

RXSYNC2

D20

VSS

D21

RXOH2

D22

TXSERCLK2

D23

NC

D24

VDD18

D25

TXCHN2_1

D26

RXSER3

E1

RRING0

E2

RGND0

E3

GNDPLL

E4

GNDPLL

E5

NC

E6

SENSE

E7

aTEST

E8

RXLOS0

E9

RXCHN0_1

E10

RXCASYNC0

E11

TXOHCLK0

E12

VDD18

E13

TXCHN0_3

E14

RXCHN1_1

E15

RXCASYNC1

E16

NC

E17

TXCHCLK1

E18

VDD18

E19

NC

E20

RXCRCSYNC2

E21

RXOHCLK2

E22

NC

E23

TXSER2

T

ABLE

1: 420 B

ALL

L

IST

BY

B

ALL

N

UMBER

P

IN

P

IN

N

AME