L831-EA Module Hardware User Manual

Page 33 of 43

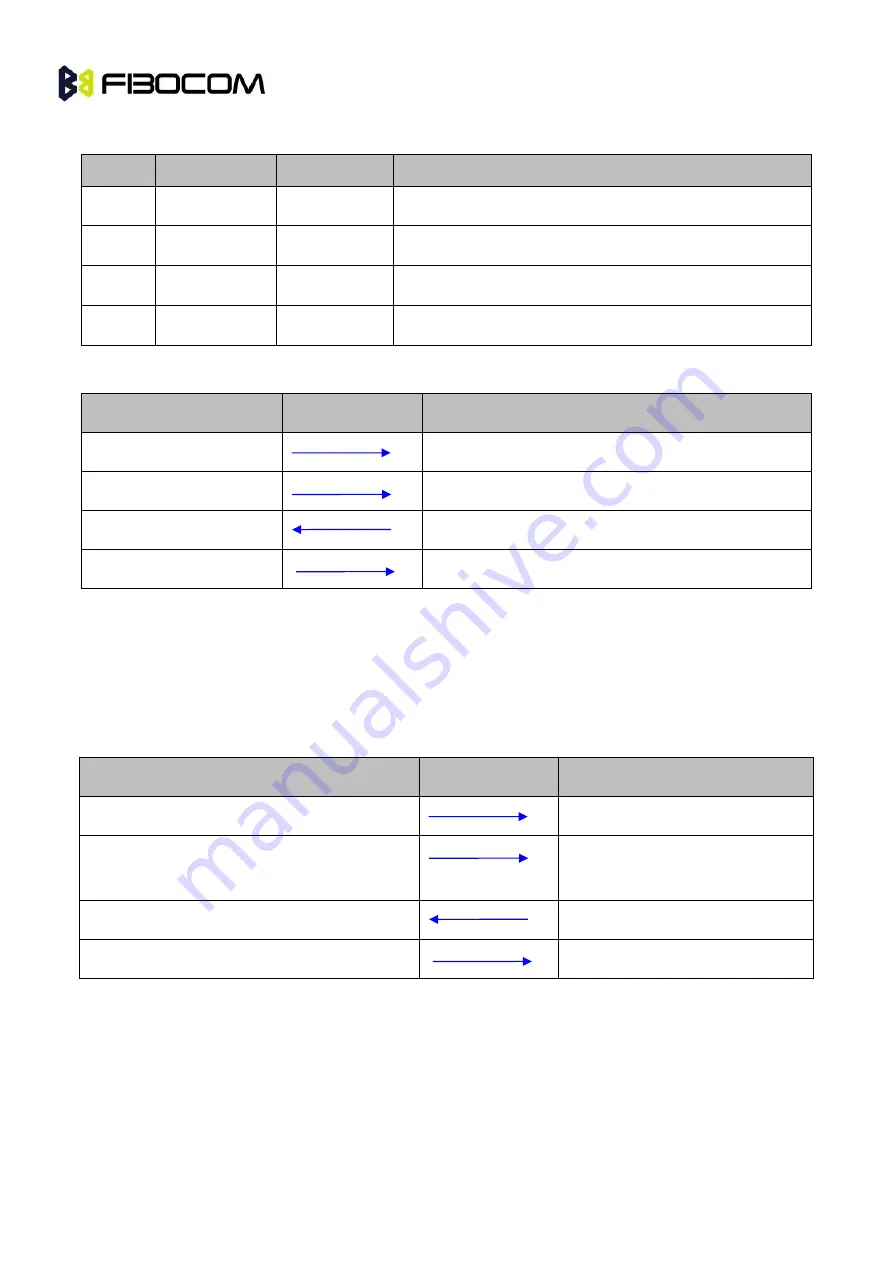

The description of I2S signal as listed below:

Pin#

Name

Type

Description

20

I2S2_CLK

O

Bit clock

28

I2S2_WA0

O

Left- right clock (LRCK)

22

I2S2_TX

O

Serial data output

24

I2S2_RX

I

Serial data input

5.6.1 Description of I2S Interface

L831-EA

Signal Direction

Audio CODEC I2S Port

I2S_CLK

I2S_CLK

I2S_WA

I2S_LRCK

I2S_RX

I2S_SDOUT

I2S_TX

I2S_SDIN

Note:

I2S interfaces can be configured to master or slave modes .

It supports various audio sample rates (48KHz, 44.1KHz, 32KHz, 24KHz, 22.5KHz, 16KHz, 12KHz,

11.025KHz, 8KHz).

5.6.2 Description of PCM Interface

L831-EA

Signal Direction

Audio CODEC PCM Port

I2S_CLK0(PCM_CLK

,

PCM clock signal)

PCM_CLK (PCM clock signal)

I2S_WA0(PCM_SYNC

,

PCM frame

synchronization signal)

PCM_SYNC (PCM frame

synchronization signal )

I2S_RX(PCM_DIN

,

PCM data input)

PCM_DOUT (PCM data output)

I2S_TX(PCM_DOUT

,

PCM data output)

PCM_DIN (PCM data input)

Description:

PCM interfaces can be configured to master or slave modes.

Supports short frame synchronization under16 bit, 32bit, 48bit and 64bit modes.

Supports sending data in burst modes and continuous modes.

Supports clock length of frame synchronization signal and rising edge/ falling edge trigger