Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved.

FIBOCOM_NL952-NA_Hardware_User_Manual

Page 29 of 57

Pin#

Pin Name

I/O Reset Value Description

Level

53

REFCLKN

I

-

PCIe Reference Clock signal

Negative

-

55

REFCLKP

I

-

PCIe Reference Clock signal

Positive

-

50

PERST#

I

PU

Asserted to reset module PCIe interface

default. If module went into coredump, it will

reset whole module, not only PCIe interface.

Active low, internal pull up(10K

Ω

)

3.3/1.8V

52

CLKREQ#

I/O PD

Asserted by device to request a PCIe

reference clock be available (active clock

state) in order to transmit data. It also used by

L1 PM Sub states mechanism, asserted by

either host or device to initiate an L1 exit.

Active low, open drain output and should add

external pull up on platform

3.3/1.8V

54

PEWAKE#

O

PD

Asserted to wake up system and reactivate

PCIe link from L2 to L0, it depends on system

whether supports wake up functionality.

Active low, open drain output and should add

external pull up on platform

3.3/1.8V

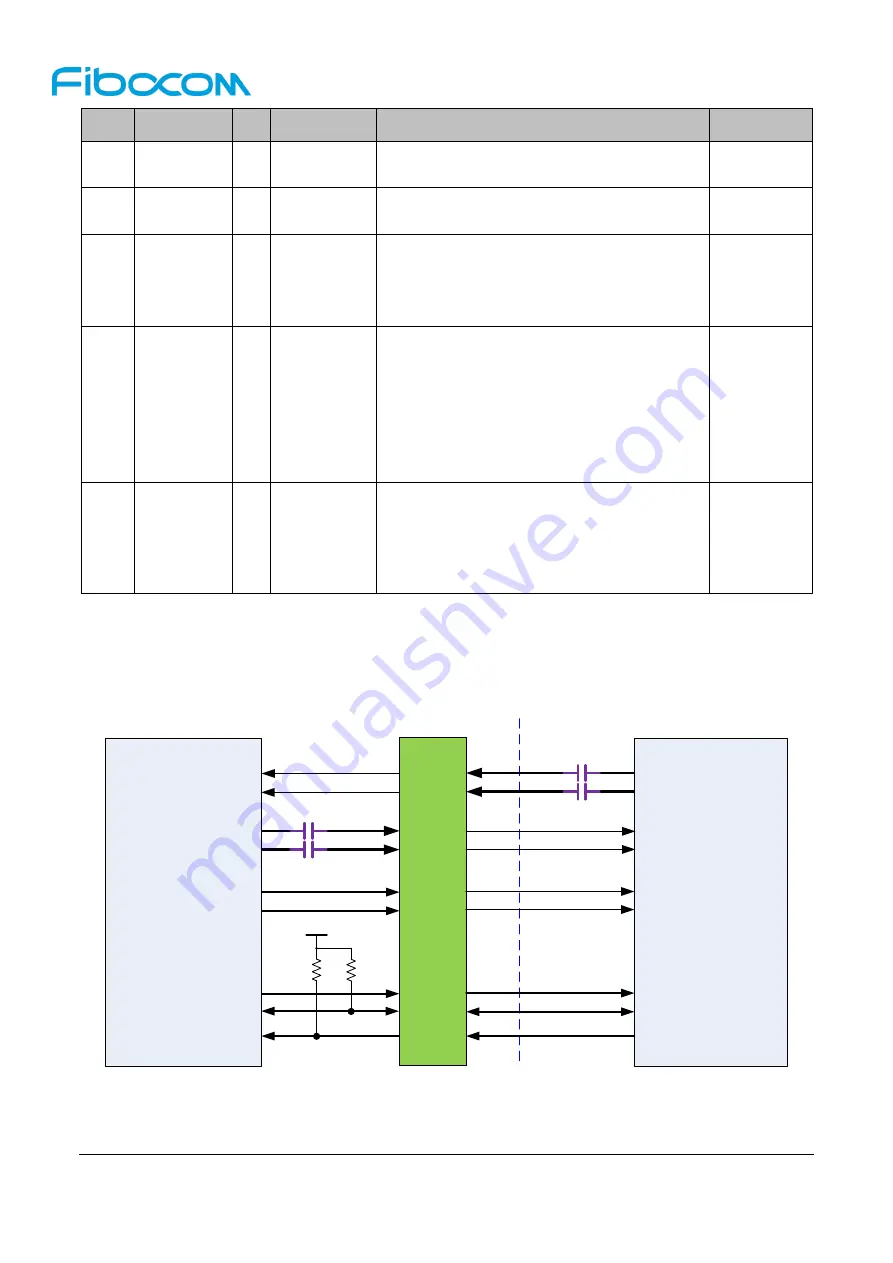

3.4.1.2 PCIe Interface Application

The reference circuit is shown in Figure 3-12:

Module side

AP side

AC Caps

AC Caps

PERST#

CLKREQ#

WAKE#

PERST#(pin50)

CLKREQ#(pin52)

PEWAKE#(pin54)

PERn0

PERP0

PETn0

PETP0

REFCLKN

REFCLKP

PETn0(pin41)

PETP0(pin43)

PERn0(pin47)

PERP0(pin49)

REFCLKN(pin53)

REFCLKP(pin55)

+3.3V/1.8V

10K

10K

M

.2

K

e

y

-B

75

p

in

C

o

n

n

e

c

to

r

Figure 3-12 Reference Circuit for PCIe Interface

NL952 module supports PCIe Gen2 interface, including three difference pairs: transmit pair TXP/N,