Reproduction forbidden without Fibocom Wireless Inc. written authorization - All Rights Reserved.

FIBOCOM_NL952-NA_Hardware_User_Manual

Page 30 of 57

receiving pair RXP/N and clock pair CLKP/N.

PCIe can achieve the maximum transmission rate of 5 GT/s, and must strictly follow the rules below in

PCB Layout:

The differential signal pair lines shall be parallel and equal in length;

The differential signal pair lines shall be short if possible and be controlled within 15 inch(380 mm) for

AP end;

The impedance of differential signal pair lines is recommended to be 100 ohm, and can be controlled

to 80

~

120 ohm in accordance with PCIe protocol;

It shall avoid the discontinuous reference ground, such as segment and space;

When the differential signal lines go through different layers, the via hole of grounding signal should

be in close to that of signal, and generally, each pair of signals require 1-3 grounding signal via holes

and the lines shall never cross the segment of plane;

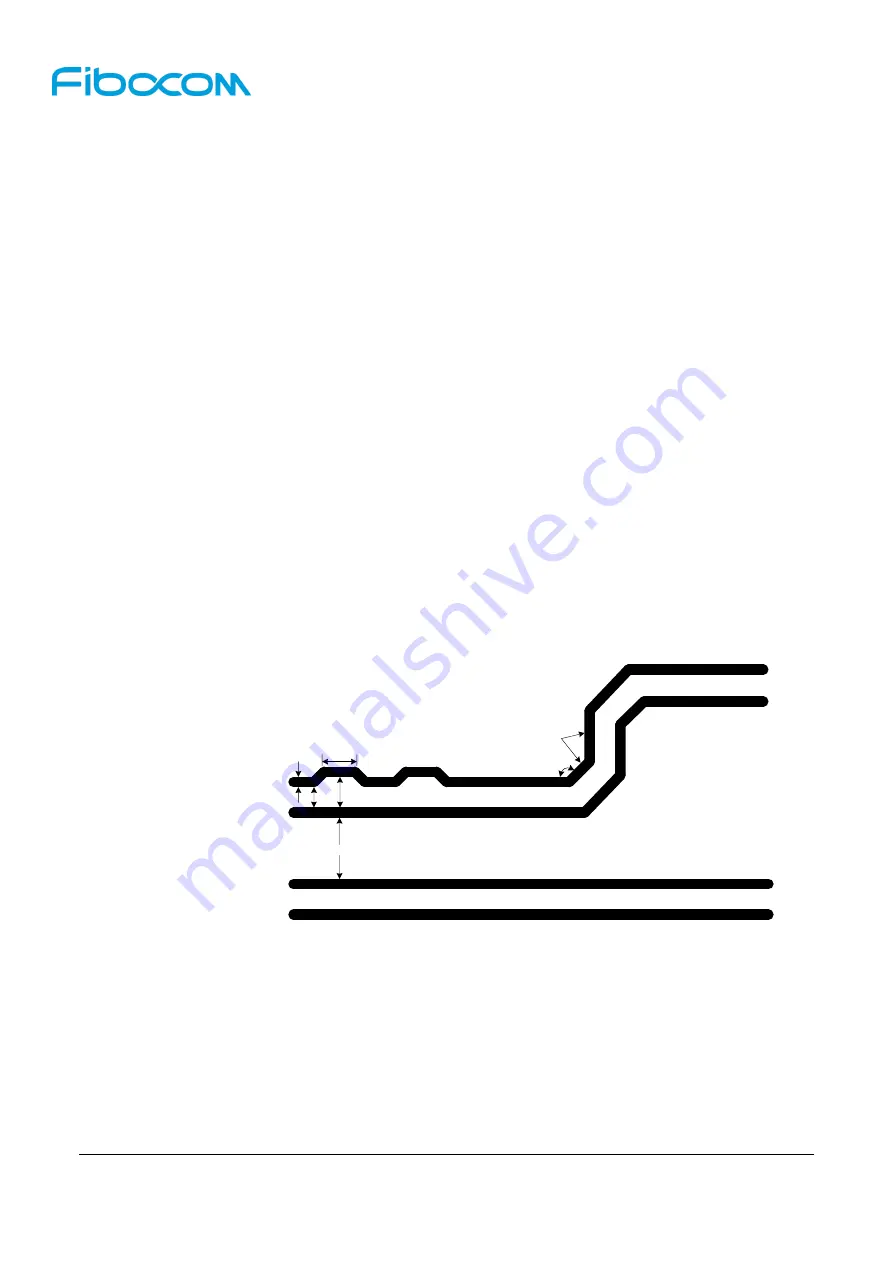

Try to avoid bended lines and avoid introducing common-mode noise in the system, which will

influence the signal integrity and EMI of difference pair. As shown in Figure 3-13, the bending angle

of all lines should be equal or greater than 135°, the spacing between difference pair lines should be

larger than 20mil, and the line caused by bending should be greater than 1.5 times line width at least.

When a serpentine line is used for length match with another line, the bended length of each segment

shall be at least 3 times the line width (≥3W). The largest spacing between the bended part of the

serpentine line and another one of the differential lines must be less than 2 times the spacing of normal

differential lines (S1<2S);

PCIe Difference Pair 1

W

S

S1<2S

≥3W

≥1

35°

≥20mil

PCIe Difference Pair 2

≥1.5W

Figure 3-13 Requirement of PCIe Line

The difference in length of two data lines in difference pair should be within 5mil, and the length match

is required for all parts. When the length match is conducted for the differential lines, the designed

position of correct match should be close to that of incorrect match, as shown in Figure 3-14. However,

there is no specific requirements for the length match of transmit pair and receiving pair, that is, the

length match is only required in the internal differential lines rather than between different difference

pairs. The length match should be close to the signal pin and pass the small-angle bending design.